- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98071 > S82451KX (INTEL CORP) SPECIALTY MICROPROCESSOR CIRCUIT, PQFP144 PDF資料下載

參數(shù)資料

| 型號(hào): | S82451KX |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQFP144 |

| 封裝: | QFP-144 |

| 文件頁數(shù): | 7/180頁 |

| 文件大?。?/td> | 1094K |

| 代理商: | S82451KX |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁

96

PRELIMINARY

82453KX/GX, 82452KX/GX, 82451KX/GX (MC)

A

1.2

DP Signals

.

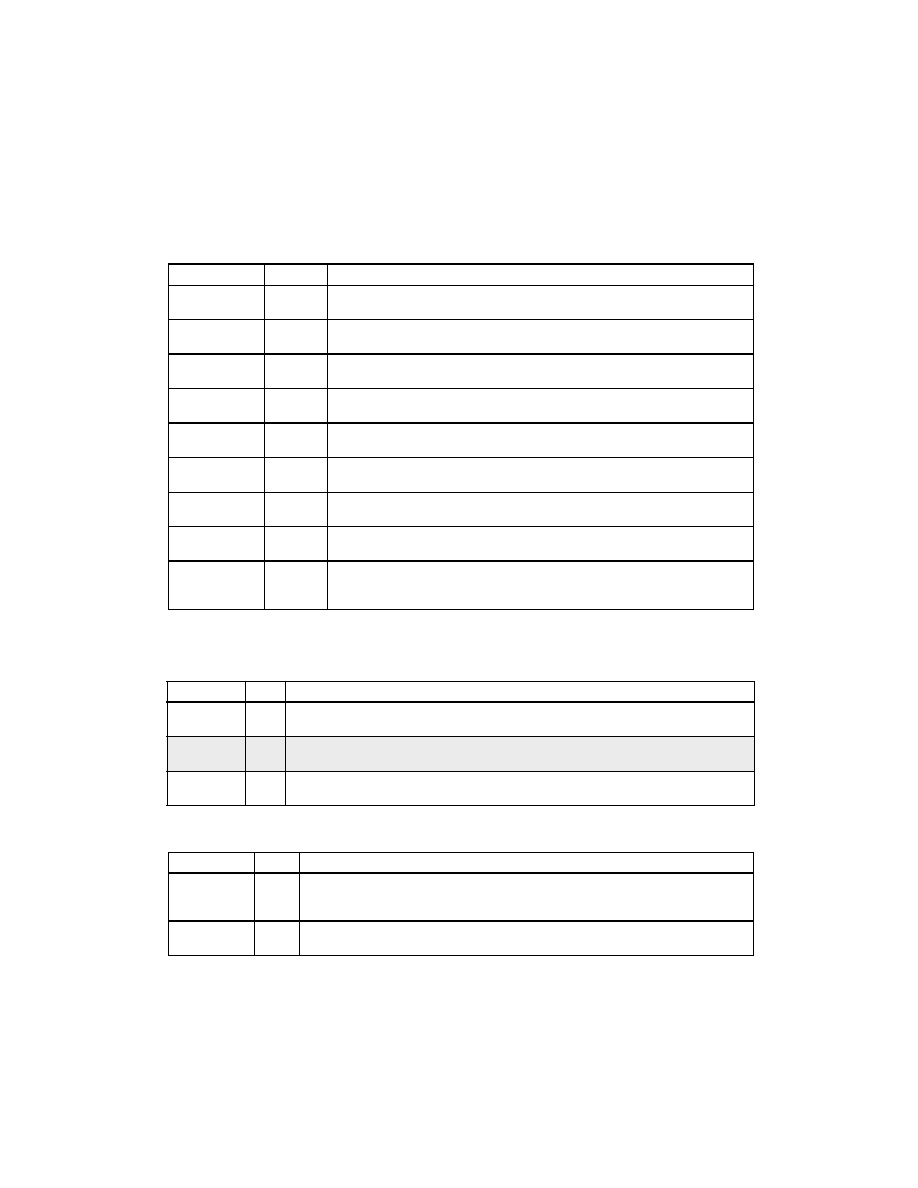

Table 7. Test Signals (DC)

Signal

Type

Description

GTLHI

I/O

GTL+

These signals must be tied to VTT using a 10K resistor for proper operation in

both test and normal operating modes.

TCK

I

CMOS

JTAG Test Clock. When TMS is tied low, this signal has no effect on normal

operation.

TDI

I

CMOS

JTAG Test Data In. When TMS is tied low, this signal has no effect on normal

operation.

TDO

O

CMOS

JTAG Test Data Out. When TMS is tied low, this signal has no effect on normal

operation.

TESTHI

I/O

TEST HIGH. These signals must be tied high using a 10K

resistor for proper

operation in both test and normal operating modes.

TESTLO

I/O

TEST LOW. These signals must be tied low using a 1K

resistor for proper

operation in both test and normal operating modes.

TMS

I

CMOS

JTAG Test Mode Select. This signal must be tied low for normal operation.

TRST#

I

CMOS

JTAG Test Reset. When TMS is tied low, this signal has no effect on normal

operation.

RECVEN

I

RECEIVER ENABLE. This function is useful for component test. This signal is

negated with PWRGOOD to disable GTL+ receivers and tri-state outputs for

board test.

Table 8. Host Bus Interface Signals (DP)

Signal

Type

Description

D[63:0]#

I/O

GTL+

DATA BUS. The data bus consists of eight bytes.

DEP[7:0]#

I/O

GTL+

DATA ECC/PARITY. DEP[7:0]# provides ECC for the D[63:0]# signals. ECC is

computed over the 64 data bits. Parity is not generated or checked by the MC.

DRDY#

I/O

GTL+

DATA READY. Asserted for each cycle that data is transferred.

Table 9. Data Path Interface Signals (DP)

Signal

Type

Description

MDE[71:0]

I/O

CMOS

MEMORY DATA AND ECC. Common to all types and sizes of memory supported,

these signals include the 64 bits of data and 8 ECC check bits. ECC is computed

over 64-bit data words. Parity is computed as byte-parity over a 64-bit word.

MDRDY0#

MDRDY1#

O

CMOS

MEMORY DATA READY (TWO COPIES). Asserted when write data on the MDE

bus is valid. Two copies are provided to support external loading.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S83296SA | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 |

| SB83296SA | 16-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP100 |

| S83C196MH | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP80 |

| S83C51FB-BB44 | 8-BIT, MROM, 24 MHz, MICROCONTROLLER, PQFP44 |

| S83C51FC-5B44 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S82452KX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Data Path Controller |

| S82453KX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM Controller |

| S82454KX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bus Interface/Controller |

| S8248P12NF | 功能描述:ANTENNA 824-896MHZ 8DBI N FML RoHS:是 類別:RF/IF 和 RFID >> RF 天線 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* |

| S82510 DIE | 制造商:Intel 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。