- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383961 > TMX320DM647ZUT720 (Texas Instruments, Inc.) Digital Media Processor PDF資料下載

參數(shù)資料

| 型號(hào): | TMX320DM647ZUT720 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Digital Media Processor |

| 中文描述: | 數(shù)字媒體處理器 |

| 文件頁數(shù): | 70/166頁 |

| 文件大?。?/td> | 1341K |

| 代理商: | TMX320DM647ZUT720 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁當(dāng)前第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁

www.ti.com

P

6.6 Enhanced Direct Memory Access (EDMA3) Controller

6.6.1

EDMA3 Channel Synchronization Events

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372–MAY 2007

The EDMA controller handles all data transfers between memories and the device slave peripherals on

the DM648 device. These data transfers include cache servicing, non-cacheable memory accesses,

user-programmed data transfers, and host accesses. These are summarized as follows:

Transfer to/from on-chip memories

–

DSP L1D memory

–

DSP L2 memory

Transfer to/from external storage

–

DDR2 SDRAM

–

Synchronous/Asynchronous EMIF (EMIFA)

Transfer to/from peripherals/hosts

–

VLYNQ

–

HPI

–

McASP

–

UART

–

Video Port 0/1/2/3/4

–

Timer 0/1/2/3

–

SPI

–

I2C

The EDMA supports up to 64 EDMA channels which service peripheral devices and external memory.

Table 6-13

lists the source of EDMA synchronization events associated with each of the programmable

EDMA channels. For the DM648 device, the association of an event to a channel is fixed; each of the

EDMA channels has one specific event associated with it. These specific events are captured in the

EDMA event registers (ER, ERH) even if the events are disabled by the EDMA event enable registers

(EER, EERH). For more detailed information on the EDMA module and how EDMA events are enabled,

captured, processed, linked, chained, and cleared, etc., see the

TMS320DM647/DM648 DSP Enhanced

DMA (EDMA) Controller User's Guide

(literature number

SPRUEL2

).

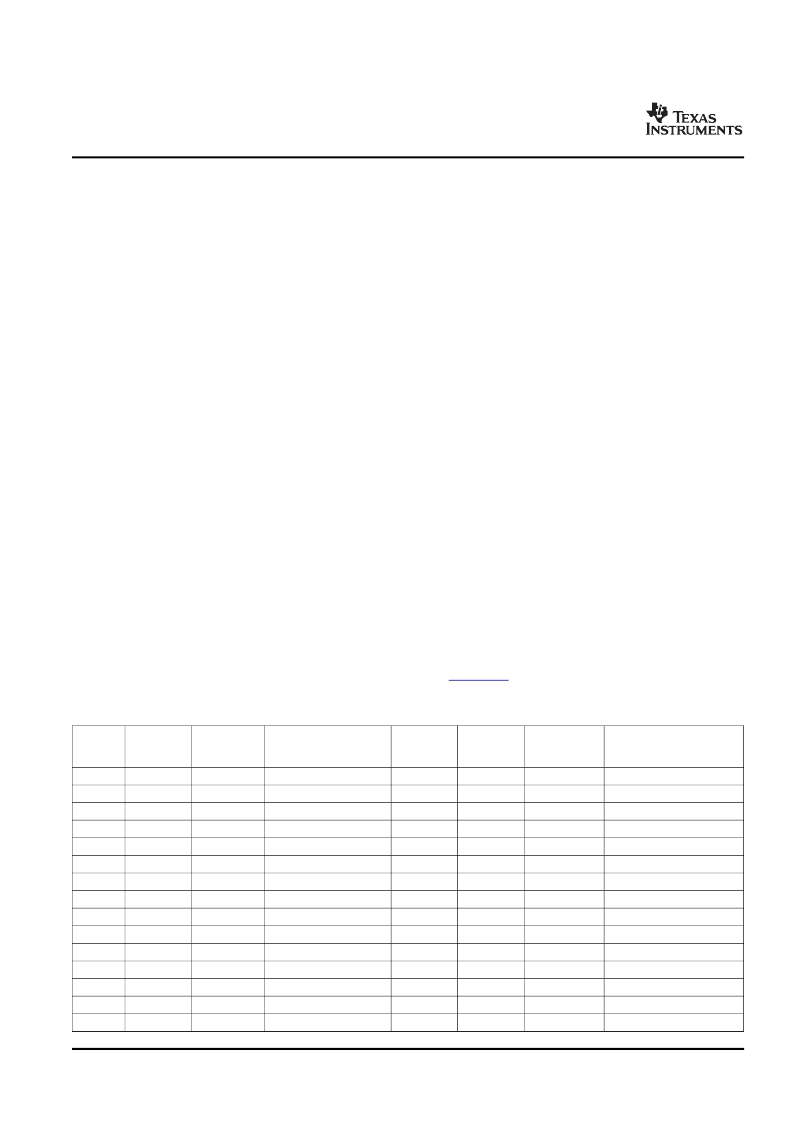

Table 6-13. EDMA Channel Synchronization Events

TPCC

CHANN

EL

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DEFAULT

EVENT#

BINARY

DEFAULT EVENT

TPCC

CHANNEL

DEFAULT

EVENT #

BINARY

DEFAULT EVENT

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

000 0000

000 0001

000 0010

000 0011

000 0100

000 0101

000 0110

000 0111

000 1000

000 1001

000 1010

000 1011

000 1100

000 1101

000 1110

HPI/PCI : DSPINT

TIMER0 : TINT0L

TIMER0 : TINT0H

TIMER2 : TINT2L

TIMER2 : TINT2H

TIMER3 : TINT3L

TIMER3 : TINT3H

IMCOP: IMXINT

IMCOP: VLCDINT

IMCOP: DSQINT

McASP: AXEVTE

McASP: AXEVTO

McASP: AXEVT

McASP: AREVTE

McASP: AREVTO

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

010 0000

010 0001

010 0010

010 0011

010 0100

010 0101

010 0110

010 0111

010 1000

010 1001

010 1010

010 1011

010 1100

010 1101

010 1110

VP2EVTYA

VP2EVTUA

VP2EVTVA

VP2EVTYB

VP2EVTUB

VP2EVTVB

VP3EVTYA

VP3EVTUA

VP3EVTVA

VP3EVTYB

VP3EVTUB

VP3EVTVB

ICREVT

ICXEVT

SPI: SPIXEVT

Peripheral Information and Electrical Specifications

70

Submit Documentation Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMX320DM647ZUT900 | Digital Media Processor |

| TMX320DM648ZUT720 | Digital Media Processor |

| TMX320DM648ZUT900 | Digital Media Processor |

| TMS320LC31PQL | DIGITAL SIGNAL PROCESSORS |

| TMX320C6414TGLZ | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320DM647ZUT900 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Media Processor |

| TMX320DM648ACUT7 | 制造商:Texas Instruments 功能描述:- Trays |

| TMX320DM648ACUT9 | 制造商:Texas Instruments 功能描述:- Trays |

| TMX320DM648AZUT7 | 制造商:Texas Instruments 功能描述: |

| TMX320DM648CUT7 | 制造商:Texas Instruments 功能描述:- Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。