- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383961 > TMX320DM647ZUT720 (Texas Instruments, Inc.) Digital Media Processor PDF資料下載

參數(shù)資料

| 型號: | TMX320DM647ZUT720 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Digital Media Processor |

| 中文描述: | 數(shù)字媒體處理器 |

| 文件頁數(shù): | 20/166頁 |

| 文件大小: | 1341K |

| 代理商: | TMX320DM647ZUT720 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁

www.ti.com

P

TMS320DM647/TMS320DM648

Digital Media Processor

SPRS372–MAY 2007

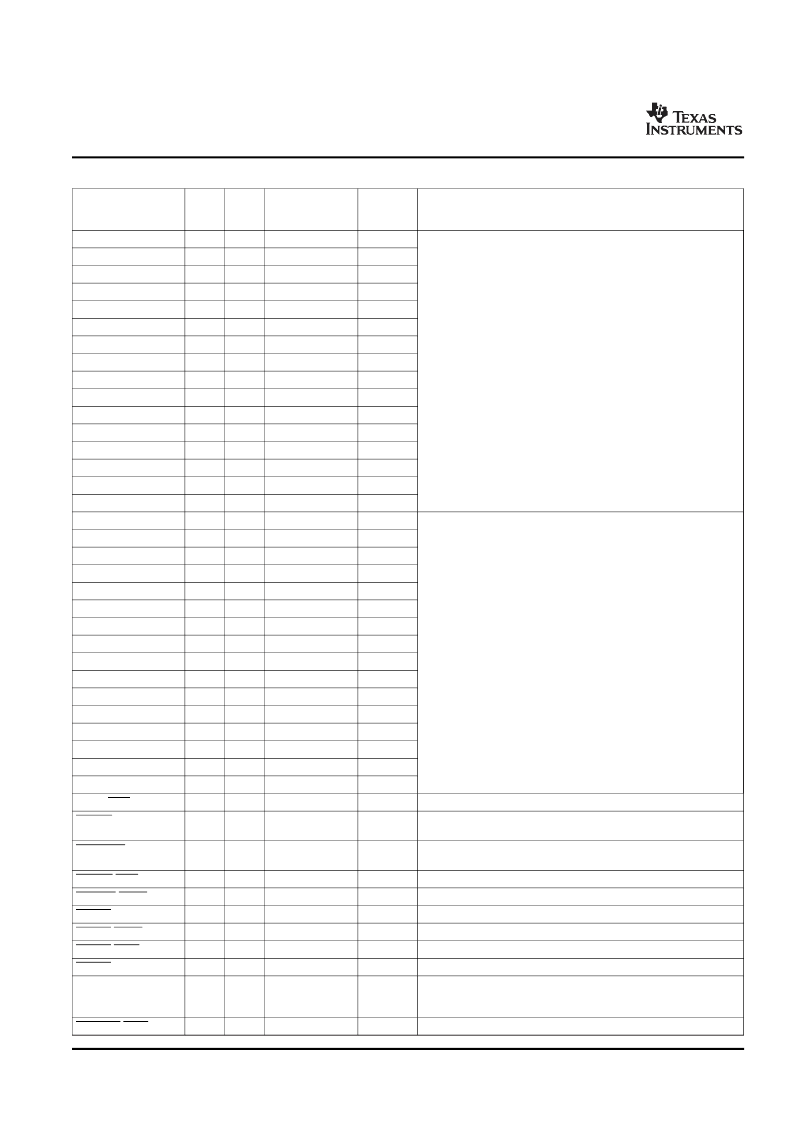

Table 2-4. TERMINAL FUNCTIONS (continued)

TERMINAL NAME

NO

TYPE

INTERNAL

PULLUP/

PULLDOWN

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPD

IPU

IPD

OPER

VOLT

DESCRIPTION

AD00/HD00

AD01/HD01

AD02/HD02

AD03/HD03

AD04/HD04

AD05/HD05

AD06/HD06

AD07/HD07

AD08/HD08

AD09/HD09

AD10/HD10

AD11/HD11

AD12/HD12

AD13/HD13

AD14/HD14

AD15/HD15

AD16/HD16

AD17/HD17

AD18/HD18

AD19/HD19

AD20/HD20

AD21/HD21

AD22/HD22

AD23/HD23

AD24/HD24

AD25/HD25

AD26/HD26

AD27/HD27

AD28/HD28

AD29/HD29

AD30/HD30

AD31/HD31

PPAR/HAS

PSTOP/HCNTL0

AA22

AB22

AC21

AA23

AC22

AB21

AA21

Y21

AB20

AA20

Y20

Y19

AB18

AA19

AC18

AA18

Y16

AB15

AA15

Y15

W15

V15

AC14

AB14

W14

V14

AC13

AB13

AA13

Y13

W13

V13

W19

Y18

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

Host Port data [15:00] pin or PCI data-address bus [15:00]

[default]

Host Port data [31:16] pin or PCI data-address bus [31:16]

[default]

Host address strobe (I) or PCI parity [default]

Host Control selects between control, address, or data registers (I)

or PCI Stop [default]

Host Control selects between control, address, or data registers (I)

or PCI Device Select [default]

Host chip select (I) or PCI parity error [default]

Host data strobe 1 (I) or PCI system error [default]

PCI command/byte enable 0 or GP[2] [default

PCI command/byte enable 1 or host data strobe 2

PCI command/byte enable 2 or host read or write select (I)

PCI command/byte enable 3 or GPIO[7]

PCI clock (I) [default] or host half-word select - first or second

half-word (not necessarily high or low order) [For HPI16 bus width

selection only] (I)

PCI frame or host interrupt from DSP to host (O/Z)

PDEVSEL/HCNTL1

Y17

I/O/Z

IPD

3.3 V

PPERR/HCS

PSERR/ HDS1

PCBE0/GP04

PCBE1/HDS2

PCBE2/HRW

PCBE3/GP07

PCLK/HHWIL

W17

W18

AC20

AC17

W16

Y14

AC15

I/O/Z

I/O/Z

I/O/Z

I

I/O/Z

I/O/Z

I/O/Z

IPU

IPU

IPU

IPU

IPU

IPU

IPU

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

3.3 V

PFRAME/HINT

AA16

I/O/Z

IPD

3.3 V

Device Overview

20

Submit Documentation Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMX320DM647ZUT900 | Digital Media Processor |

| TMX320DM648ZUT720 | Digital Media Processor |

| TMX320DM648ZUT900 | Digital Media Processor |

| TMS320LC31PQL | DIGITAL SIGNAL PROCESSORS |

| TMX320C6414TGLZ | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320DM647ZUT900 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Digital Media Processor |

| TMX320DM648ACUT7 | 制造商:Texas Instruments 功能描述:- Trays |

| TMX320DM648ACUT9 | 制造商:Texas Instruments 功能描述:- Trays |

| TMX320DM648AZUT7 | 制造商:Texas Instruments 功能描述: |

| TMX320DM648CUT7 | 制造商:Texas Instruments 功能描述:- Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。