- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1961 > PI7C8154BNAIE (Pericom)IC PCI-PCI BRIDGE ASYNC 304-PBGA PDF資料下載

參數(shù)資料

| 型號: | PI7C8154BNAIE |

| 廠商: | Pericom |

| 文件頁數(shù): | 73/114頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC PCI-PCI BRIDGE ASYNC 304-PBGA |

| 產(chǎn)品變化通告: | Product Discontinuation Notice 22/Jan/2010 |

| 標準包裝: | 27 |

| 系列: | * |

| 應(yīng)用: | * |

| 接口: | * |

| 電源電壓: | * |

| 封裝/外殼: | 304-BBGA |

| 供應(yīng)商設(shè)備封裝: | 304-PBGA(31x31) |

| 包裝: | 管件 |

| 安裝類型: | 表面貼裝 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

PI7C8154B

ASYNCHRONOUS 2-PORT

PCI-to-PCI BRIDGE

Advance Information

Page 61 of 114

JUNE 2008 REVISION 1.1

S_PERR#

Transaction Type

Direction

Bus Where Error

Was Detected

Primary/ Secondary Parity

Error Response Bits

1

Delayed Write

Downstream

Secondary

x / x

02

Delayed Write

Upstream

Primary

1 / 1

0

Delayed Write

Upstream

Secondary

x / 1

Note: x=don’t care

2

=The parity error was detected on the target (secondary) bus but not on the initiator (primary) bus.

Table 5-7 shows assertion of P_SERR#. This signal is set under the following conditions:

PI7C8154B has detected P_PERR# asserted on an upstream posted write transaction or

S_PERR# asserted on a downstream posted write transaction.

PI7C8154B did not detect the parity error as a target of the posted write transaction.

The parity error response bit on the command register and the parity error response bit on the

bridge control register must both be set.

The SERR# enable bit must be set in the command register.

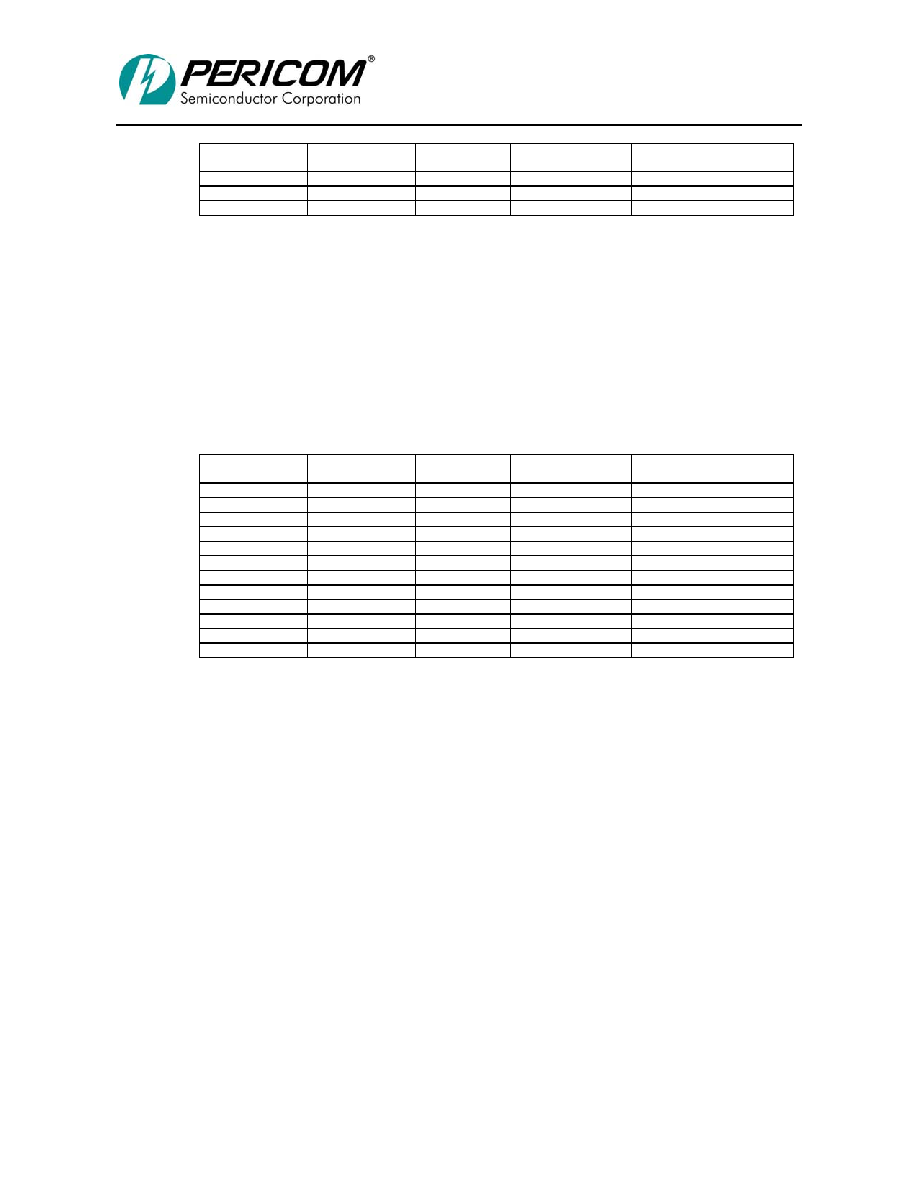

Table 5-7 ASSERTION OF P_SERR# FOR DATA PARITY ERRORS

P_SERR#

Transaction Type

Direction

Bus Where Error

Was Detected

Primary / Secondary Parity

Error Response Bits

1 (de-asserted)

Read

Downstream

Primary

x / x

1

Read

Downstream

Secondary

x / x

1

Read

Upstream

Primary

x / x

1

Read

Upstream

Secondary

x / x

1

Posted Write

Downstream

Primary

x / x

02 (asserted)

Posted Write

Downstream

Secondary

1 / 1

03

Posted Write

Upstream

Primary

1 / 1

1

Posted Write

Upstream

Secondary

x / x

1

Delayed Write

Downstream

Primary

x / x

1

Delayed Write

Downstream

Secondary

x / x

1

Delayed Write

Upstream

Primary

x / x

1

Delayed Write

Upstream

Secondary

x / x

Note: x=don’t care

5.4

SYSTEM ERROR (SERR#) REPORTING

PI7C8154B uses the P_SERR# signal to report conditionally a number of system error conditions

in addition to the special case parity error conditions described in Section 5.2.3.

Whenever assertion of P_SERR# is discussed in this document, it is assumed that the following

conditions apply:

For the bridge to assert P_SERR# for any reason, the SERR# enable bit must be set in the

command register.

Whenever the bridge asserts P_SERR#, PI7C8154B must also set the signaled system error bit

in the status register.

In compliance with the PCI-to-PCI Bridge Architecture Specification, the bridge asserts P_SERR#

when it detects the secondary SERR# input, S_SERR#, asserted and the SERR# forward enable bit

is set in the bridge control register. In addition, the bridge also sets the received system error bit in

the secondary status register.

The bridge also conditionally asserts P_SERR# for any of the following reasons:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C9X110BNBE | IC PCIE TO PCI REV BRG 160LFBGA |

| PI7C9X130DNDE | IC PCIE-PCIX BRIDGE 1PORT 256BGA |

| PI7C9X20303SLCFDE | IC PCIE PACKET SWITCH 128LQFP |

| PI7C9X20303ULAZPE | IC PCIE PACKET SWITCH 132TQFN |

| PI7C9X20404GPBNBE | IC PCIE PACKET SWITCH 148LFBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C8154EVB | 功能描述:界面開發(fā)工具 64B/66MHz 2 Port PCI Bridge Eval Brd RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| PI7C8154NA-33 | 制造商:PERICOM 功能描述: |

| PI7C81552 | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:ENHANCED 2-PORT PCI TO PCI BRIDGE INTEL 21152 COMPARISON |

| PI7C81552A | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:ENHANCED 2-PORT PCI TO PCI BRIDGE INTEL 21152 COMPARISON |

| PI7C9X110 | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:PCI Express-to-PCI Reversible Bridge |

發(fā)布緊急采購,3分鐘左右您將得到回復。