- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379802 > CD1283 (Intel Corp.) IEEE 1284-Compatible Parallel Interface PDF資料下載

參數(shù)資料

| 型號(hào): | CD1283 |

| 廠商: | Intel Corp. |

| 英文描述: | IEEE 1284-Compatible Parallel Interface |

| 中文描述: | 符合IEEE 1284兼容并行接口 |

| 文件頁數(shù): | 85/94頁 |

| 文件大?。?/td> | 1237K |

| 代理商: | CD1283 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁當(dāng)前第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁

IEEE 1284-Compatible Parallel Interface

—

CD1283

Datasheet

85

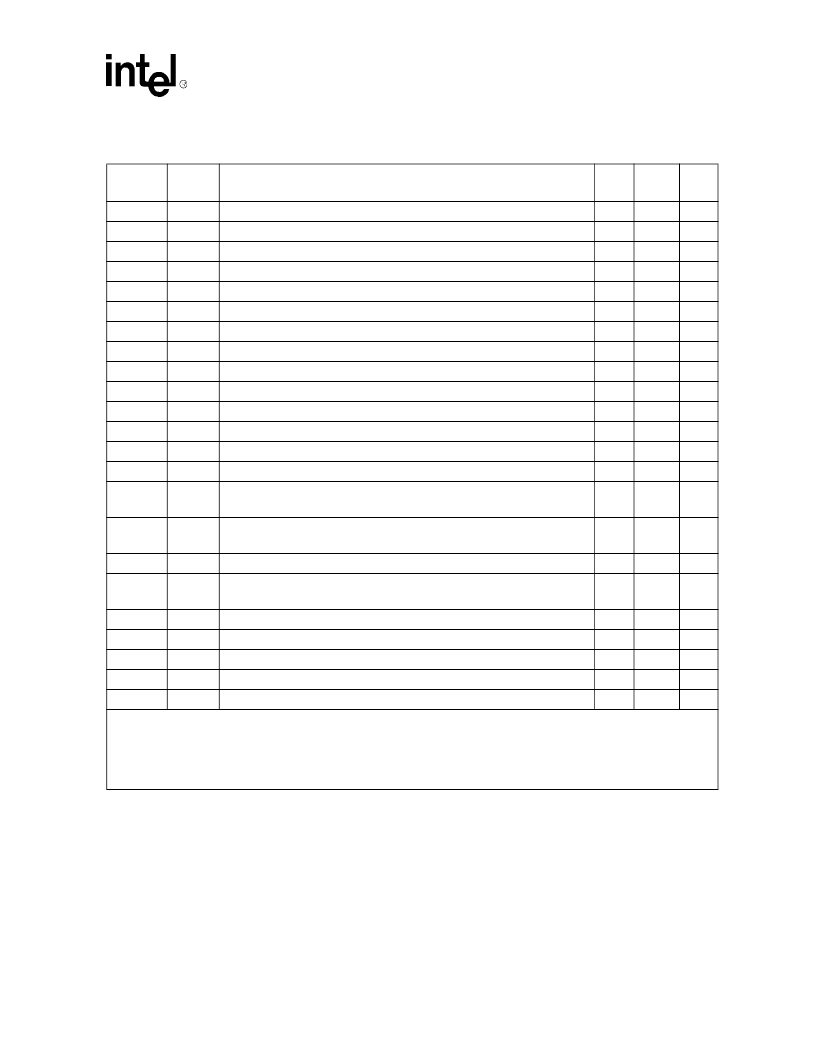

Table 13. Synchronous Timing Reference Parameters

Timing

Number

Figure

Parameter

MIN

MAX

Unit

t

1

26

Setup time, CS* and DS* to C1 rising edge

15

ns

t

2

26

Setup time, R/W* to C1 rising edge

15

ns

t

3

26

Setup time, address valid to C1 rising edge

20

ns

t

4

26

C2 rising edge to data valid

60

ns

t

5

26

DTACK* low from C3 rising edge

1

30

ns

t

6

26

CS* and DS* trailing edge to data bus high-impedance

30

ns

t

7

26

CS* and DS* inactive between host accesses

10

ns

t

8

26

Hold time, R/W* after C3 rising edge

20

ns

t

9

26

Hold time, address valid after C3 rising edge

0

ns

t

10

27

Setup time, write data valid to C2 rising edge

0

ns

t

11

28

Setup time, DS* and DGRANT* to C1 rising edge

30

ns

t

12

28

Setup time, SVCACK* to DS* and DGRANT*

10

ns

t

13

27

Hold time, write data valid after C3 rising edge

0

ns

t

14

29

Propagation delay, DS* and DGRANT* to DPASS*

35

ns

t

15

29

30

Falling edge DMAREQ* after rising edge CLK (DMA write/read)

25

ns

t

16

29

30

Hold time, rising edge DMAREQ* after falling edge DMAACK*

(DMA write/read)

20

ns

t

17

29

Setup time, data valid before rising edge C3 (DMA write)

5

ns

t

18

29

30

Setup time, falling edge DMAACK* to falling edge C1 (DMA write/read)

10

ns

t

21

26

DTACK* active pull-up time

2

t

22

30

Hold time, data valid after rising edge C3 (DMA write)

5

t

23

30

Hold time, data valid after rising edge C1 (DMA read)

10

30

t

24

30

Data valid after falling edge C1 (DMA read)

25

t

25

30

Inactive time, DMAACK* (DMA read)

10

NOTES:

1. On host I/O cycles immediately following SVCACK* cycles and writes to the EOSRR, DTACK* will be delayed by 20 CLKs (1

ms @ 20 MHz, 800 ns @ 25 MHz). On systems that do not use DTACK* to signal the end of the I/O cycle, use wait states or

some other form of delay generation to assure that the CD1283 is not accessed until after this time period.

2. DTACK* sources current (drives

‘

high

’

) until the voltage on the DTACK* line is approximately 1.5 V; then DTACK* enters the

‘

open-drain

’

(high-impedance) state.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CD1284 | IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports |

| CD13002 | NPN SILICON PLANAR EPITAXIAL, HIGH VOLTAGE FAST SWITCHING POWER TRANSISTOR |

| CD14538 | CMOS DUAL PRECISION MONOSTABLE MULTIVIBRATOR |

| CD14538BMS | CMOS Dual Precision Monostable Multivibrator |

| CD15B-15MB | CD105B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CD1284 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports |

| CD-12AFFM-QL8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12AFFM-QR8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12AMMM-QL8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12BFFA-LL7001 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。