- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379802 > CD1283 (Intel Corp.) IEEE 1284-Compatible Parallel Interface PDF資料下載

參數(shù)資料

| 型號(hào): | CD1283 |

| 廠商: | Intel Corp. |

| 英文描述: | IEEE 1284-Compatible Parallel Interface |

| 中文描述: | 符合IEEE 1284兼容并行接口 |

| 文件頁數(shù): | 53/94頁 |

| 文件大小: | 1237K |

| 代理商: | CD1283 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當(dāng)前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁

IEEE 1284-Compatible Parallel Interface

—

CD1283

Datasheet

53

7.0

Detailed Register Descriptions

This section presents a detailed description of each register. Registers have two formats: full eight

bits, where the entire content defines a single function; or the register is a collection of bits,

grouped singly or in multiples, defining a function. In the second case, the descriptions divide the

register into its component parts and describe the bits individually. The registers are presented in

the same order as outlined in

Chapter 4.0

. Bits defined as

‘

0

’

should not be modified and, if values

other than

‘

0

’

are read, program execution should not be affected or software compatibility with

future revisions will be uncertain.

7.1

Global Registers

7.1.1

Access Enable Register

The AER provides binary compatibility with the CD1284. Users must program this register with

the least-significant bits set to

‘

0

’

to access the parallel channel; however, to perform a device reset

through the RCR, AER must = 02h. The contents of the upper 5 bits should be ignored when read.

7.1.2

Global Firmware Revision Code Register

The GFRCR serves two purposes in the CD1283. First, it displays the revision number of the

firmware in the device. When a revision to the CD1283 is required, the revision number of the

firmware is increments by one. The revision code is 24 (hex) for the Revision D device, and 25

(hex) for the Revision E device.

Secondly, this register can be used by the system programmer as an indication of when the internal

processor has completed reset procedures, after either a power-on reset (through the RESET*

input) or a software global reset (through the reset command in the CCR). Immediately after the

reset operation begins, the internal CPU clears the register. When complete, and the CD1283 is

ready to accept host accesses, the register is loaded with the revision code.

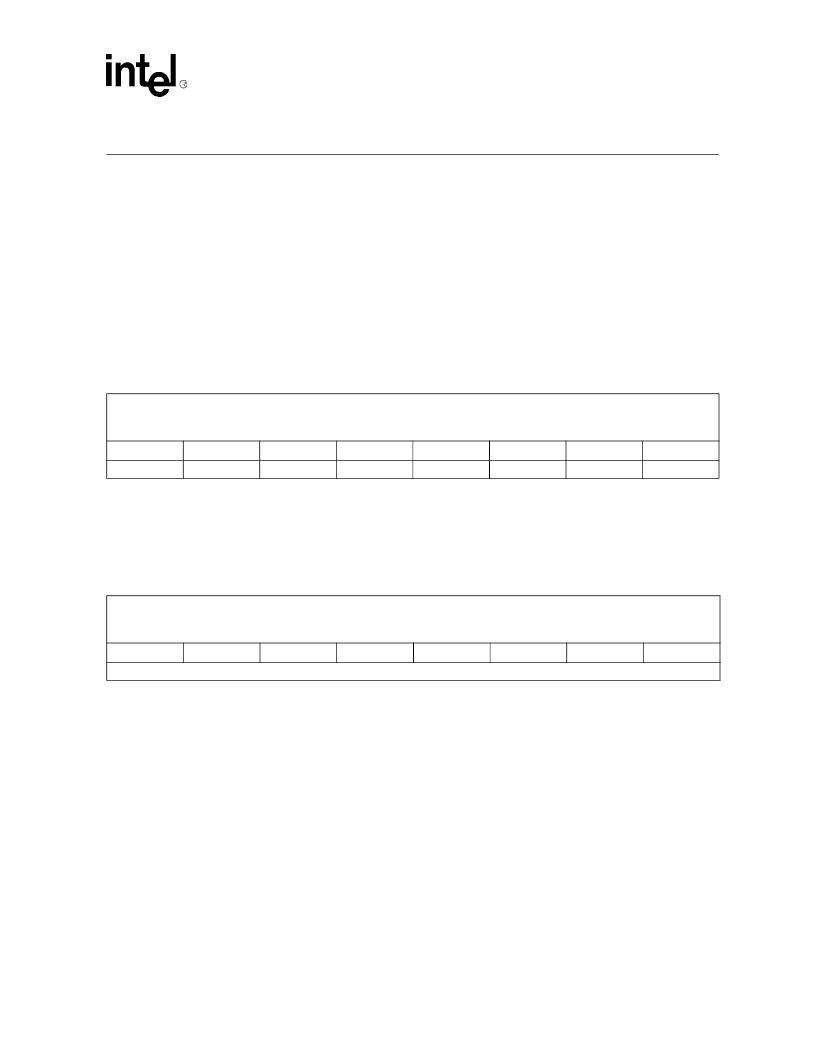

Register Name: AER

Register Description: Access Enable

Access: R/W

8-Bit Hex Address: 68

Default Value: XX

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

X

X

X

X

X

0

0

0

Register Name: GFRCR

Register Description: Global Firmware Revision Code

Access: R/W

8-Bit Hex Address: 4F

Default Value: 25

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Firmware Revision Code

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CD1284 | IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports |

| CD13002 | NPN SILICON PLANAR EPITAXIAL, HIGH VOLTAGE FAST SWITCHING POWER TRANSISTOR |

| CD14538 | CMOS DUAL PRECISION MONOSTABLE MULTIVIBRATOR |

| CD14538BMS | CMOS Dual Precision Monostable Multivibrator |

| CD15B-15MB | CD105B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CD1284 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports |

| CD-12AFFM-QL8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12AFFM-QR8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12AMMM-QL8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12BFFA-LL7001 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。