- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379802 > CD1283 (Intel Corp.) IEEE 1284-Compatible Parallel Interface PDF資料下載

參數(shù)資料

| 型號: | CD1283 |

| 廠商: | Intel Corp. |

| 英文描述: | IEEE 1284-Compatible Parallel Interface |

| 中文描述: | 符合IEEE 1284兼容并行接口 |

| 文件頁數(shù): | 19/94頁 |

| 文件大小: | 1237K |

| 代理商: | CD1283 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁

IEEE 1284-Compatible Parallel Interface

—

CD1283

Datasheet

19

4.0

Register Summary

Local CPU communication with the CD1283 occurs through a register set. Within this register set,

there are four types of registers:

Global, common to all functions of the device

Parallel pipeline

Parallel port

Service-acknowledge accessible

Global registers are always available to the CPU and their addresses are not affected by the

contents of the AER (this register is provided to maintain compatibility with the CD1284)

.

Note:

AER must be set to

‘

00h

’

and must not be changed (except to access RCR), or access to many

registers will not work properly!

The following tables define the register names, read and write access modes, internal address

offsets, and bit definitions. A detailed description of each register, its contents and functions can be

found in

Chapter 7.0

The address offset defined is the binary value that should be applied to the

address inputs (A[6:0]) during I/O cycles.

Note that the addresses are shown relative to the CD1283 definition of address lines. In 16- and 32-

bit systems, it is a common practice to connect 8-bit peripherals to only one byte lane. Thus, in 16-

bit systems, the CD1283 appears at every other address (for example, the CD1283 A[0] input is

connected to CPU A[1]). In 32-bit systems, the CD1283 appears at every fourth address (CD1283

A[0] is connected to CPU A[2]). In either of these cases, the address used by the programmer will

be different than what is shown in the tables. For instance, in a 16-bit Motorola

68000-based

system, the CD1283 is placed on data lines D[7:0], which are at odd addresses in the Motorola

scheme of addressing. The CD1283 A[0] input is connected with A[1] of the 68000, A[1] with

A[2], and so on. Thus, the CD1283 address 0x40 becomes 0x81 to the programmer. It is left-

shifted one bit and A[0] must be

‘

1

’

for low-byte (D[7:0]) accesses.

4.1

Register Summary Tables

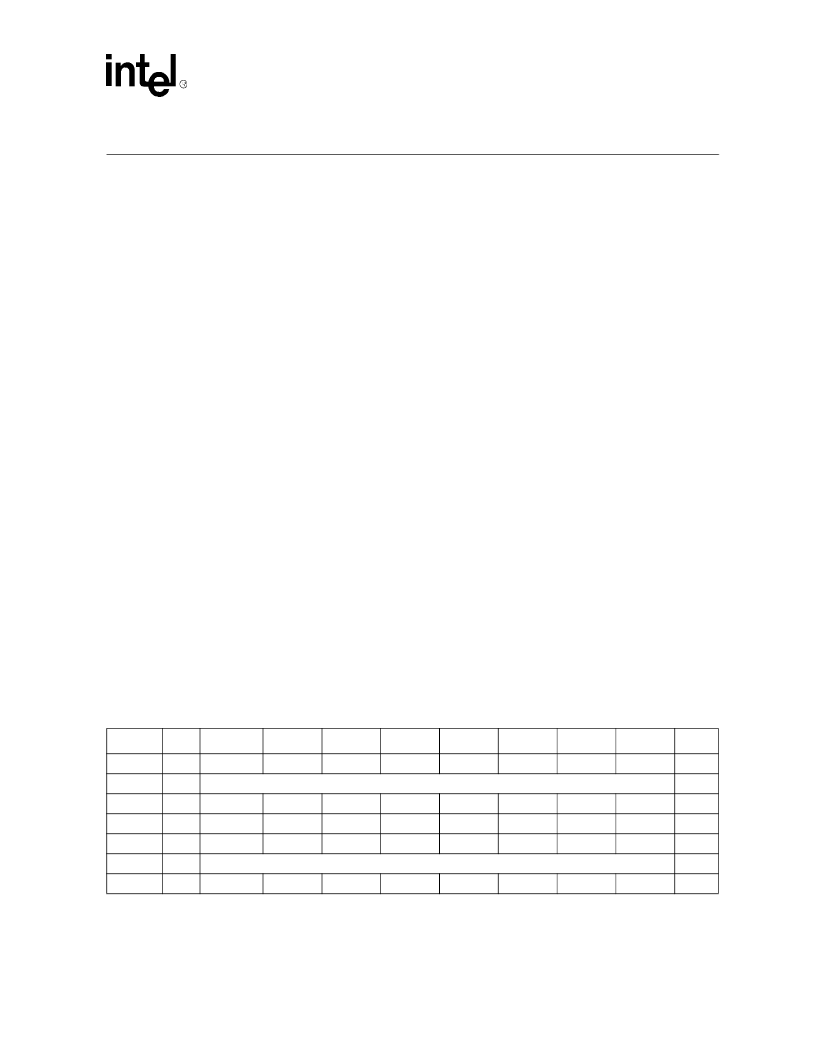

Table 1. Global Registers

Name

Hex

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Page

AER

68

Poll

Poll

Poll

Poll

Poll

0

0

0

53

GFRCR

4F

Firmware Revision Code

53

GPDIR

71

Dir 7

Dir 6

Dir 5

Dir 4

Dir 3

Dir 2

Dir 1

Dir 0

54

GPIO

70

Data 7

Data 6

Data 5

Data 4

Data 3

Data 2

Data 1

Data 0

54

PIR

61

PPIreq

PPort

Pipeline

0

0

0

0

0

54

PPR

7E

Binary Value

55

SVRR

67

DMAREQ

n/u

n/u

n/u

SRP

n/u

n/u

n/u

55

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CD1284 | IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports |

| CD13002 | NPN SILICON PLANAR EPITAXIAL, HIGH VOLTAGE FAST SWITCHING POWER TRANSISTOR |

| CD14538 | CMOS DUAL PRECISION MONOSTABLE MULTIVIBRATOR |

| CD14538BMS | CMOS Dual Precision Monostable Multivibrator |

| CD15B-15MB | CD105B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CD1284 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports |

| CD-12AFFM-QL8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標準包裝:10 |

| CD-12AFFM-QR8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標準包裝:10 |

| CD-12AMMM-QL8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標準包裝:10 |

| CD-12BFFA-LL7001 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標準包裝:10 |

發(fā)布緊急采購,3分鐘左右您將得到回復。