- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379802 > CD1283 (Intel Corp.) IEEE 1284-Compatible Parallel Interface PDF資料下載

參數(shù)資料

| 型號(hào): | CD1283 |

| 廠商: | Intel Corp. |

| 英文描述: | IEEE 1284-Compatible Parallel Interface |

| 中文描述: | 符合IEEE 1284兼容并行接口 |

| 文件頁(yè)數(shù): | 17/94頁(yè) |

| 文件大小: | 1237K |

| 代理商: | CD1283 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)

IEEE 1284-Compatible Parallel Interface

—

CD1283

Datasheet

17

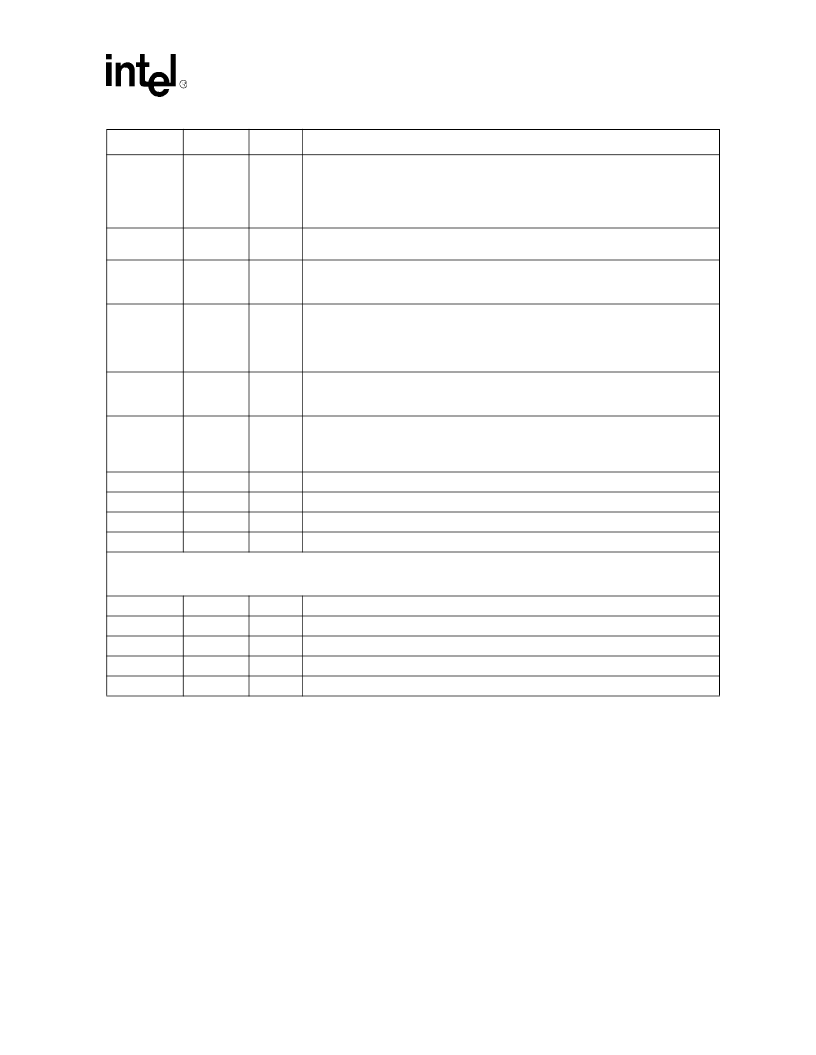

SVCREQP*

68

OD

ACTIVE-LOW SERVICE REQUEST PARALLEL:

This is an open-drain output and

must be tied to external V

through a pull-up resistor. Note that this output is only acti-

vated by certain conditions on the parallel port (such as, negotiation changes, direction

changes, etc.). SVCREQP* is not activated by FIFO threshold, or FIFO full/empty con-

ditions (refer to

Chapter 5.0

for information on how to use DMAREQ* to implement a

fully interrupt-driven system).

SVCACKP*

69

I

ACTIVE-LOW SERVICE ACKNOWLEDGE PARALLEL:

This input must not be driven

active except in response to a parallel service request presented by the device.

DGRANT*

70

I

ACTIVE-LOW DAISY GRANT:

This input is driven active during service acknowledge

cycles to enable the daisy-chain function. This input, when qualified with DS* and a

valid service acknowledge (SVCACKP*), activates the service acknowledge cycle.

DPASS*

71

O

ACTIVE-LOW DAISY PASS:

This output is driven active during service acknowledge

cycles to enable the next device in the daisy-chain. It is driven active when no valid

service request exists and the service acknowledge input is active. In multiple CD1283

designs, this signal is normally connected to the DGRANT* input of the next device in

the chain.

PD[7:0]

41

–

48

I/O

PARALLEL PORT DATA LINES [7:0]:

Bidirectional, depending on the protocol being

used, these signals are used to transfer data over the interface between the master

and slave.

GP[7:0]

53

–

60

I/O

GENERAL-PURPOSE I/O [7:0]:

General-purpose input/output port data lines. These

signals are individually direction-programmable, acting as inputs or outputs. The

direction of each signal is controlled by the corresponding bit in the GPDIR register.

Control/status of the actual signals is provided through the GPIO register.

A_1284

31

I

ACTIVE-HIGH 1284 ACTIVE INPUT:

(SLCTIN* in Compatibility mode).

nInit

34

I

ACTIVE-LOW INIT SIGNAL:

(INIT* in Compatibility mode).

HstBsy

32

I

ACTIVE-HIGH HOST BUSY SIGNAL:

(AUTOFD* in Compatibility mode).

HstClk

33

I

ACTIVE-LOW HOST CLOCK SIGNAL:

(STROBE* in Compatibility mode).

NOTE:

The above four parallel handshake signals are driven by the master in an IEEE Std 1284 interface, and as such are

inputs to the CD1283. Their functions depend on the transfer protocol selected. Refer to the IEEE Std 1284-1994

document for protocol functions. (See

Chapter 10.0

for ordering information.)

PerClk

37

O

ACTIVE-LOW PERIPHERAL CLOCK:

(ACK* in Compatibility mode)

PerBsy

36

O

ACTIVE-HIGH PERIPHERAL BUSY:

(BUSY in Compatibility mode)

AkDaRq

35

O

ACKNOWLEDGE DATA REQUEST:

(PERROR* in Compatibility mode)

Xflag

39

O

EXTENSIBILITY FLAG:

(SELECT in Compatibility mode)

nDatAv

38

O

ACTIVE-LOW DATA AVAILABLE SIGNAL:

(FAULT* in Compatibility mode)

Symbol

Pin No.

Type

Description

(Sheet 2 of 3)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CD1284 | IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports |

| CD13002 | NPN SILICON PLANAR EPITAXIAL, HIGH VOLTAGE FAST SWITCHING POWER TRANSISTOR |

| CD14538 | CMOS DUAL PRECISION MONOSTABLE MULTIVIBRATOR |

| CD14538BMS | CMOS Dual Precision Monostable Multivibrator |

| CD15B-15MB | CD105B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CD1284 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:IEEE 1284-Compatible Parallel Interface Controller with Two High-Speed Asynchronous Serial Ports |

| CD-12AFFM-QL8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12AFFM-QR8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12AMMM-QL8D01 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

| CD-12BFFA-LL7001 | 功能描述:MIDDLE 制造商:amphenol ltw 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:10 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。