- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383876 > T7698 (Lineage Power) Quad T1/E1 Line Interface and Octal T1/E1 Monitor(四T1/E1線(xiàn)接口和八T1/E1監(jiān)控器) PDF資料下載

參數(shù)資料

| 型號(hào): | T7698 |

| 廠商: | Lineage Power |

| 英文描述: | Quad T1/E1 Line Interface and Octal T1/E1 Monitor(四T1/E1線(xiàn)接口和八T1/E1監(jiān)控器) |

| 中文描述: | 四T1/E1線(xiàn)路接口和八路的T1/E1監(jiān)視器(四個(gè)T1/E1線(xiàn)接口和八T1/E1的監(jiān)控器) |

| 文件頁(yè)數(shù): | 67/112頁(yè) |

| 文件大小: | 1359K |

| 代理商: | T7698 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)當(dāng)前第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)

Data Sheet

January 1999

T7698 Quad T1/E1 Line Interface and Octal T1/E1 Monitor

67

Lucent Technologies Inc.

Frame Monitors

(continued)

Alarms and Performance Monitoring

(continued)

4.

Blue alarm

or the

alarm indication signal

(AIS). The alarm indication signal (AIS), sometimes referred to as

the blue alarm, is an indication that the remote end is out of service. The T7698 detects an incoming alarm

indication signal as defined in Table 39.

5.

The

continuous E-bit

alarm (CON-E) is asserted when the receive frame monitor detects:

I.

Five consecutive seconds where each one-second interval contains

≥

991 received E bits = 0 events.

II.

Simultaneously, no LFA or LMFA occurred.

III. Optionally, no A bit = 1 was received*.

IV. Optionally, neither Sa6-F

hex

nor Sa6-E

hex

codes were detected*.

The five-second timer is started when:

I.

CRC-4 multiframe alignment is achieved, and

II.

Optionally, A = 0 is detected, and

III. Optionally, neither Sa6

_

F

hex

nor Sa6

_

E

hex

is detected.

The five-second counter is restarted and the continuous E-bit alarm is disabled when:

I.

LFA or LMFA occurs, or

II.

≤

990 E bit = 0 events occurred in 1 second, or

III. Optionally, an A bit = 1, is detected, or

IV. Optionally, a valid Sa6_F

hex

or Sa6_E

hex

code was detected.

* Options can be set through register Framer_PR1.

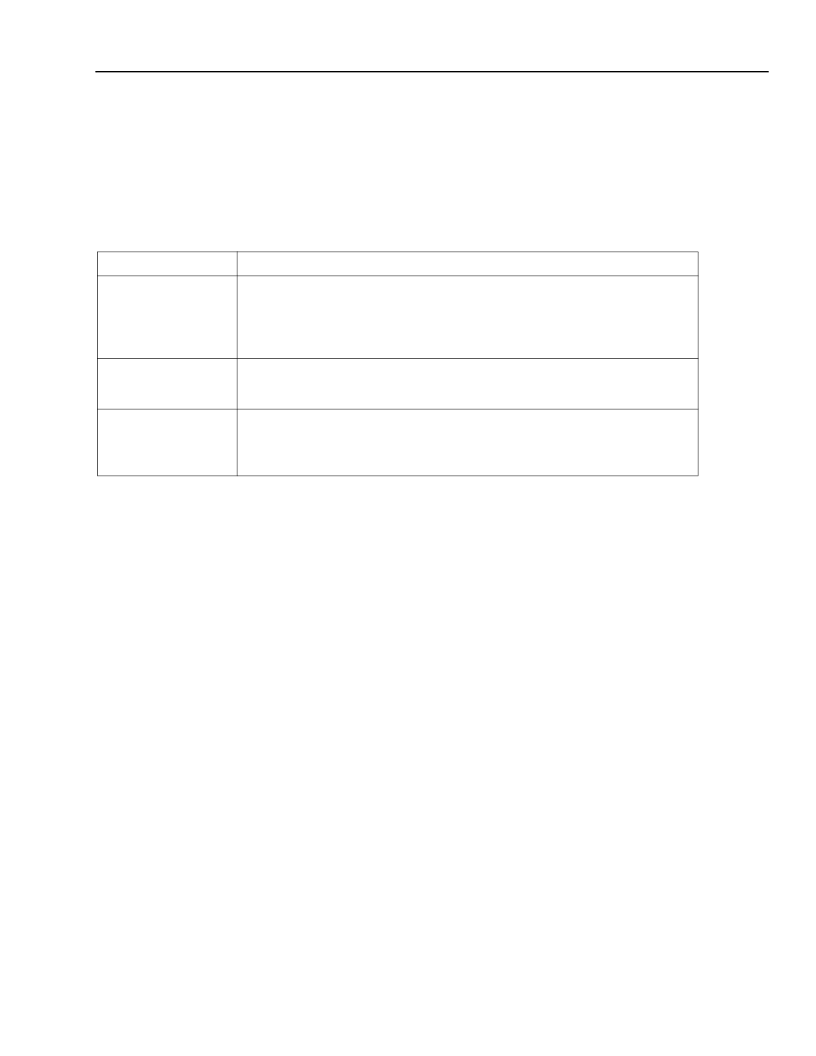

Table 39. Alarm Indication Signal Conditions

Framing Format

DS1

Remote Frame Alarm Format

As indicated in ANSI TI.231_1997, the receive frame monitor detects an

unframed signal with a 1s density of at least 99.9% for a period of 3 ms. The

AIS defect is terminated when a signal is detected as not meeting either the

99.9% 1s density or the unframed signal criteria for a period of

3 ms.

As described in Draft prETS 300 233:1992 Section 8.2.2.4, loss of frame

alignment occurs and the frame monitor receives a 512 bit period containing

two (2) or less binary zeros.

As described in ITU Rec. G.775, the incoming signal has two (2) or fewer

zeros in each of two consecutive double frame periods (512 bits). AIS is

cleared if each of two consecutive double frame periods contains three (3) or

more zeros or frame alignment signal (FAS) has been found.

CEPT ETSI

CEPT ITU

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7705A | SUPPLY-VOLTAGE SUPERVISORS |

| T8100A | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線(xiàn)時(shí)間段交換機(jī)) |

| T8100 | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線(xiàn)時(shí)隙交換機(jī)) |

| T8102 | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線(xiàn)時(shí)隙交換機(jī)) |

| T8105 | H.100/H.110 Interface and Time-Slot Interchanger(H.100/H.110接口和干線(xiàn)時(shí)隙交換機(jī)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T77 | 制造商:Thomas & Betts 功能描述:2-1/2"CONDUIT BODY,IRON,T,F-7 制造商:Cooper Crouse-Hinds 功能描述: 制造商:Thomas & Betts 功能描述:Fittings T-Fitting 2.5inch Non-Thread Iron |

| T7700 | 制造商:INTEL 制造商全稱(chēng):Intel Corporation 功能描述:Core2 Duo Processors and Core2 Extreme Processors for Platforms Based on Mobile 965 Express Chipset Family |

| T77000150 | 制造商:Assembly Value Added 功能描述: |

| T7705102CA | 制造商:Texas Instruments 功能描述: |

| T7705A | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:SUPPLY-VOLTAGE SUPERVISORS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。