- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383682 > OMAP5910(RISC) Dual-Core Processor PDF資料下載

參數(shù)資料

| 型號: | OMAP5910(RISC) |

| 英文描述: | Dual-Core Processor |

| 中文描述: | 雙核處理器 |

| 文件頁數(shù): | 48/160頁 |

| 文件大?。?/td> | 1997K |

| 代理商: | OMAP5910(RISC) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁

Functional Overview

36

August 2002 Revised August 2003

SPRS197B

3.2

MPU Memory Maps

3.2.1 MPU Global Memory Map

The MPU has a unified address space. Therefore, the internal and external memories for program and data

as well as peripheral registers and configuration registers are all accessed within the same address space.

The MPU space is always addressed using byte addressing. Table 31 provides a high level illustration of

the entire MPU addressable space. Further detail regarding the peripheral and configuration registers is

provided in Sections 3.2.2, 3.15, and 3.17.

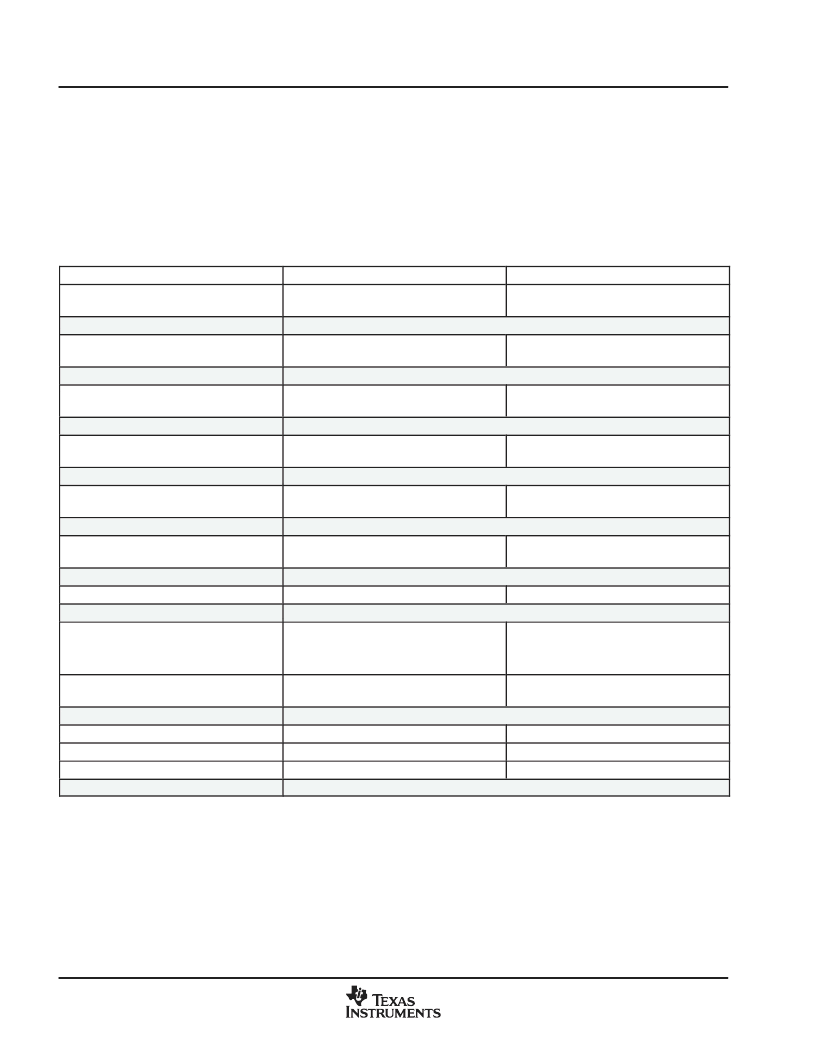

Table 31. OMAP5910 MPU Global Memory Map

BYTE ADDRESS RANGE

ON-CHIP

EXTERNAL INTERFACE

0x0000 0000 0x01FF FFFF

EMIFS (Flash CS0)

32M bytes

0x0200 0000 0x03FF FFFF

Reserved

0x0400 0000 0x05FF FFFF

EMIFS (Flash CS1)

32M bytes

0x0600 0000 0x07FF FFFF

Reserved

0x0800 0000 0x09FF FFFF

EMIFS (Flash CS2)

32M bytes

0x0A00 0000 0x0BFF FFFF

Reserved

0x0C00 0000 0x0DFF FFFF

EMIFS (Flash CS3)

32M bytes

0x0E00 0000 0x0FFF FFFF

Reserved

0x1000 0000 0x13FF FFFF

EMIFF (SDRAM)

64M bytes

0x1400 0000 0x1FFF FFFF

Reserved

0x2000 0000 0x2002 FFFF

IMIF Internal SRAM

192K bytes

0x2003 0000 0x2FFF FFFF

Reserved

0x3000 0000 0x5FFF FFFF

Local Bus space for USB Host

0x6000 0000 0xDFFF FFFF

Reserved

0xE000 0000 0xE0FF FFFF

DSP public memory space

(accessible via MPUI)

16M bytes

0xE100 0000 0xEFFF FFFF

DSP public peripherals

(accessible via MPUI)

0xF000 0000 0xFFFA FFFF

Reserved

0xFFFB 0000 0xFFFB FFFF

MPU public peripherals

0xFFFC 0000 0xFFFC FFFF

MPU/DSP shared peripherals

0xFFFD 0000 0xFFFE FFFF

MPU private peripherals

0xFFFF 0000 0xFFFF FFFF

Reserved

Some peripherals within this memory region are actually shared peripherals (UART 1,2,3).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OMC506 | Closed Loop Speed Controller For 3-Phase Brushless DC Motor MP-3T Package |

| OMC507 | 5 Amp. Push-Pull 3-Phase Brushless DC Motor Controller Driver(5A,推挽三相無刷直流電機控制驅(qū)動器) |

| OMC510 | 36V Hi-Rel Three-Phase Brushless DC Motor Controller in a PCB-1 package |

| OMC510 | DSP-Based Three-Phase Brushless DC Motor Controller(基于DSP的三相無刷直流電機控制器) |

| OMD100F60HL | TRANSISTOR | IGBT POWER MODULE | HALF BRIDGE | 600V V(BR)CES | 150A I(C) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OMAP5912 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Applications Processor |

| OMAP5912GDYAR | 制造商:Texas Instruments 功能描述:- Tape and Reel |

| OMAP5912ZDY | 功能描述:處理器 - 專門應(yīng)用 Applications Processor RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| OMAP5912ZDYA | 制造商:Texas Instruments 功能描述:APPLICATIONS PROCESSOR - Trays |

| OMAP5912ZZG | 功能描述:處理器 - 專門應(yīng)用 Applications Processor RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。