- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383682 > OMAP5910(RISC) Dual-Core Processor PDF資料下載

參數(shù)資料

| 型號(hào): | OMAP5910(RISC) |

| 英文描述: | Dual-Core Processor |

| 中文描述: | 雙核處理器 |

| 文件頁(yè)數(shù): | 42/160頁(yè) |

| 文件大?。?/td> | 1997K |

| 代理商: | OMAP5910(RISC) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)

Introduction

30

August 2002 Revised August 2003

SPRS197B

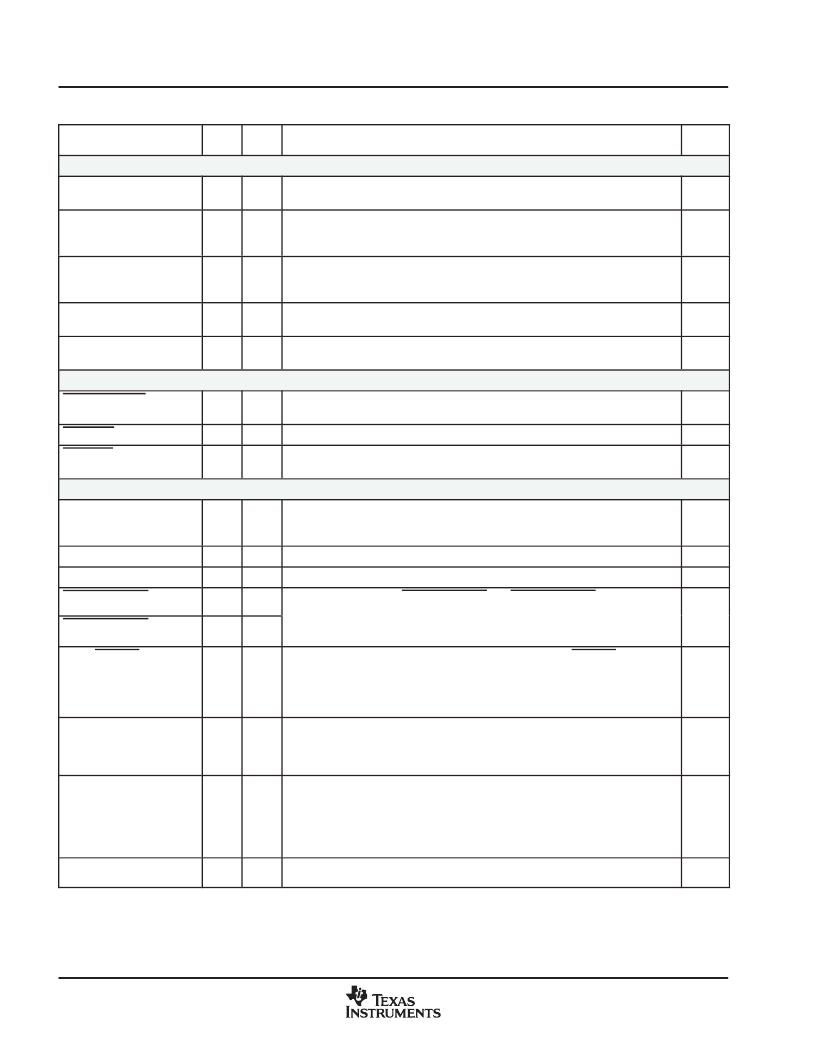

Table 24. Signal Description (Continued)

GDY

BALL

SIGNAL

TYPE

DESCRIPTION

GZG

BALL

Device Clock Pins (Continued)

OSC1_OUT

W3

P3

Base crystal XO connection. Analog output from base oscillator for use with

external 12- or 13-MHz crystal.

analog

MCLK

Y9

U7

M-Clock. General-purpose clock output which may be configured to run at 12 MHz

or 48 MHz. MCLK may be configured to drive constantly or only when the

MCLKREQ signal is asserted active high.

O

BCLK

Y13

P11

B-Clock. General purpose clock output which may be configured to run at

12 MHz. BCLK may be configured to drive constantly or only when the BCLKREQ

signal is asserted active high.

O

MCLKREQ

R10

N8

M-Clock Request. Active high request input which allows an external device to

request that MCLK be driven.

I

BCLKREQ

R13

L10

B-Clock Request. Active high request input which allows an external device to

request that BCLK be driven.

I

Reset Logic Pins

PWRON_RESET

G19

F14

Reset input to device. Active-low asynchronous reset input resets the entire

OMAP5910 device.

I

MPU_RST

V15

P12

MPU reset input. Active-low asynchronous reset input resets the MPU core.

I

RST_OUT

W15

M11

Reset output. Active-low output is asserted when MPUST is active (after

synchronization.)

O

Interrupts and Miscellaneous Control and Configuration Pins

MPU_BOOT

AA17

R12

MPU boot mode. When MPU_BOOT is low, the MPU boots from chip select 0 of

the EMIFS (Flash) interface. When MPU_BOOT is high, the MPU boots from chip

select 3 of EMIFS.

I

DMA_REQ_OBS

L14

H12

DMA request external observation output.

O

IRQ_OBS

M18

J13

IRQ external observation output.

O

EXT_DMA_REQ1

T19

N15

External DMA requests. EXT_DMA_REQ0 and EXT_DMA_REQ1 provide two

DMA request inputs which external devices may use to trigger System DMA

transfers. The System DMA must be configured in software to respond to these

external requests.

I

EXT_DMA_REQ0

N15

N17

BFAIL/EXT_FIQ

W19

R14

Battery power failure and external FIQ interrupt input. BFAIL/EXT_FIQ may be

used to gate certain input pins when battery power is low or failing. The pins which

may be gated are configured via software. This pin can also optionally be used as

an external FIQ interrupt source to the MPU. The function of this pin is

configurable via software.

I

EXT_MASTER_REQ

R10

N8

External master request. If the 12-MHz clock is provided by an external device

instead of using the on-chip oscillator, a high level on this output indicates to the

external device that the clock must be driven. A low level indicates that the

OMAP5910 device is in sleep mode and the 12-MHz clock is not necessary.

O

LOW_PWR

T20

L13

Low-power request output. This active-high output indicates that the OMAP5910

device is in a low-power sleep mode. During reset and functional modes,

LOW_PWR is driven low. This signal can be used to indicate a low-power state to

external power management devices in a system or it can be used as a chip

select to external SDRAM memory to minimize current consumption while the

SDRAM is in self-refresh and the OMAP5910 device is in sleep mode.

O

CONF

V18

T16

Configuration input. CONF selects reserved factory test modes. CONF should

always be pulled low during device operation.

I

I = Input, O = Output, Z = High-Impedance

All core voltage supplies should be tied to the same voltage level (within 0.3 V). During system prototyping phases, it may be useful to maintain

a capability for independent measurement of core supply currents to facilitate power optimization experiments.

§See Sections 5.6.1 and 5.6.2 for special VSS considerations with oscillator circuits.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OMC506 | Closed Loop Speed Controller For 3-Phase Brushless DC Motor MP-3T Package |

| OMC507 | 5 Amp. Push-Pull 3-Phase Brushless DC Motor Controller Driver(5A,推挽三相無(wú)刷直流電機(jī)控制驅(qū)動(dòng)器) |

| OMC510 | 36V Hi-Rel Three-Phase Brushless DC Motor Controller in a PCB-1 package |

| OMC510 | DSP-Based Three-Phase Brushless DC Motor Controller(基于DSP的三相無(wú)刷直流電機(jī)控制器) |

| OMD100F60HL | TRANSISTOR | IGBT POWER MODULE | HALF BRIDGE | 600V V(BR)CES | 150A I(C) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OMAP5912 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Applications Processor |

| OMAP5912GDYAR | 制造商:Texas Instruments 功能描述:- Tape and Reel |

| OMAP5912ZDY | 功能描述:處理器 - 專門應(yīng)用 Applications Processor RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| OMAP5912ZDYA | 制造商:Texas Instruments 功能描述:APPLICATIONS PROCESSOR - Trays |

| OMAP5912ZZG | 功能描述:處理器 - 專門應(yīng)用 Applications Processor RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。