- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98068 > S1C6S460D 4-BIT, MROM, 2 MHz, MICROCONTROLLER, UUC124 PDF資料下載

參數(shù)資料

| 型號: | S1C6S460D |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, 2 MHz, MICROCONTROLLER, UUC124 |

| 封裝: | 4.69 X 4.68 MM, DIE-124 |

| 文件頁數(shù): | 13/107頁 |

| 文件大小: | 788K |

| 代理商: | S1C6S460D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁

S1C6S460 TECHNICAL MANUAL

EPSON

5

CHAPTER 2: CPU AND BUILT-IN MEMORY

CHAPTER

2 CPU AND BUILT-IN MEMORY

2.1 CPU and Instruction Set

The S1C6S460 uses the 4-bit core CPU S1C6200 for its CPU. It has almost the same register configurations,

instructions, and other features as the other family devices which use the S1C6200/6200A/6200B, allow-

ing full use of software assets. The instruction set of the S1C6S460 has 108 types of instructions, all

consisting of one word (12 bits).

For detailed information on the CPU and the instruction set, refer to the "S1C6200/6200A Core CPU

Manual".

Note, however, that because S1C6S460 does not assume SLEEP operation, the SLP instruction is not

available in the S1C6200 instruction set.

The instruction list is shown in Tables 2.1.1(a)–(c).

The following lists the symbols used in the instruction list:

Symbols associated with registers and memory

A

A register

B

B register

X

XHL register

(low order eight bits of index register IX)

Y

YHL register

(low order eight bits of index register IY)

XH

XH register

(high order four bits of XHL register)

XL

XL register

(low order four bits of XHL register)

YH

YH register

(high order four bits of YHL register)

YL

YL register

(low order four bits of YHL register)

XP

XP register

(high order four bits of index register IX)

YP

YP register

(high order four bits of index register IY)

SP

Stack pointer SP

SPH

High-order four bits of stack pointer SP

SPL

Low-order four bits of stack pointer SP

MX, M(X)

Data memory whose address is specified

with index register IX

MY, M(Y)

Data memory whose address is specified

with index register IY

Mn, M(n)

Data memory address 000H–00FH

(address specified with immediate data n of

00H–0FH)

M(SP)

Data memory whose address is specified

with stack pointer SP

r, q

Two-bit register code

r, q is two-bit immediate data; according to

the contents of these bits, they indicate

registers A, B, and MX and MY (data

memory whose addresses are specified with

index registers IX and IY)

Symbols associated with program counter

NBP

New bank pointer

NPP

New page pointer

PCB

Program counter bank

PCP

Program counter page

PCS

Program counter step

PCSH

Four high order bits of PCS

PCSL

Four low order bits of PCS

Symbols associated with flags

F

Flag register (I, D, Z, C)

C

Carry flag

Z

Zero flag

D

Decimal flag

I

Interrupt flag

↓

Flag reset

↑

Flag set

Flag set or reset

Associated with immediate data

p

Five-bit immediate data or label 00H–1FH

s

Eight-bit immediate data or label 00H–0FFH

l

Eight-bit immediate data 00H–0FFH

i

Four-bit immediate data 00H–0FH

Associated with arithmetic and other operations

+

Add

-

Subtract

∧

Logical AND

∨

Logical OR

Exclusive-OR

5

Add-subtract instruction for decimal operation

when the D flag is set

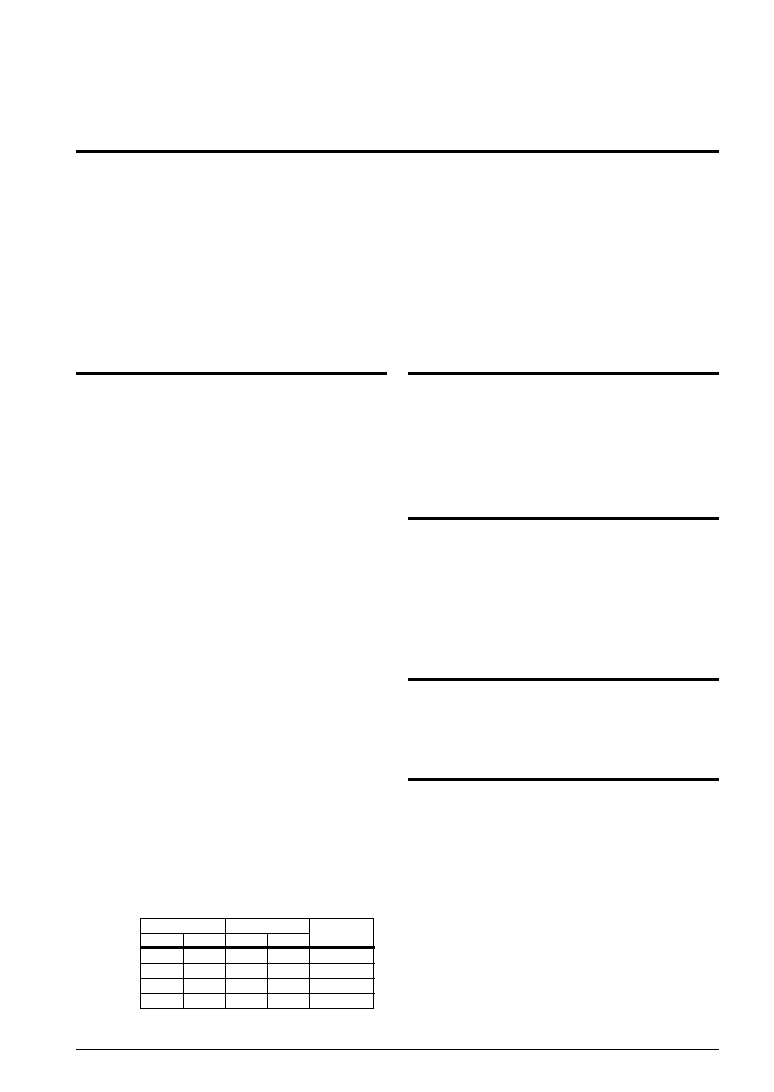

rq

Register

r1

r0

q1

q0

specified

0

000

A

0

101

B

1

010

MX

1

111

MY

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1C88104P0A0100 | 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, PBGA240 |

| S1C88317D0A0100 | MICROCONTROLLER, UUC170 |

| S1C88308D0A0100 | MICROCONTROLLER, UUC170 |

| S1C88308F0A0100 | MICROCONTROLLER, PQFP160 |

| S1C88348F | 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, PQFP16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1C7309X | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:B/W CCD PROCESSOR |

| S1C7309X01 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:B/W CCD PROCESSOR |

| S1C88349 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88649 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88650 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。