- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄253142 > 92909-032HLF 32 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER PDF資料下載

參數(shù)資料

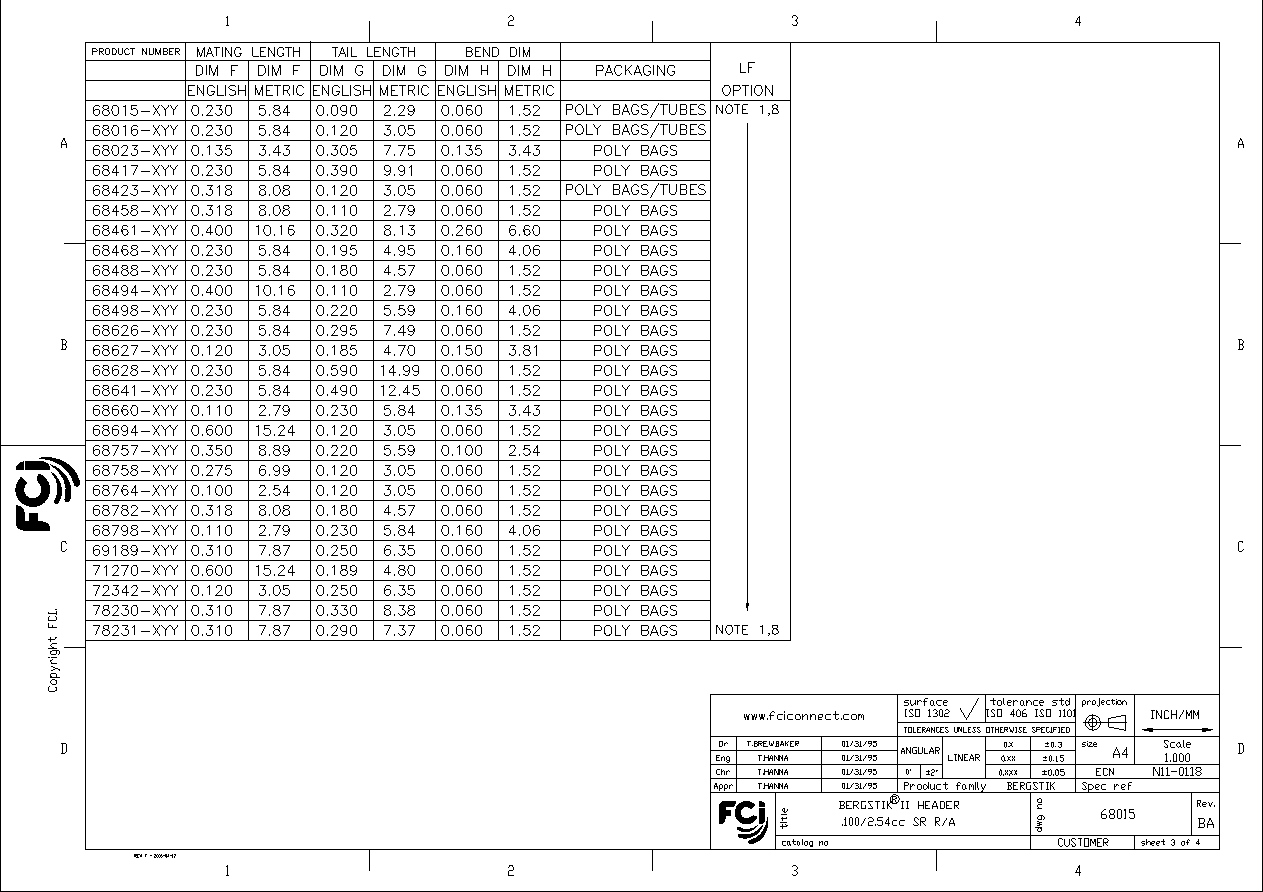

| 型號(hào): | 92909-032HLF |

| 元件分類(lèi): | 電路板相疊連接器 |

| 英文描述: | 32 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

| 封裝: | LEAD FREE |

| 文件頁(yè)數(shù): | 3/4頁(yè) |

| 文件大小: | 324K |

| 代理商: | 92909-032HLF |

PDM: Rev:BA

Released

.

STATUS:

Printed: Apr 20, 2011

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 92909-033HLF | 33 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

| 92909-034HLF | 34 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

| 92909-035HLF | 35 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

| 92909-036HLF | 36 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

| 92909-101HLF | 1 CONTACT(S), MALE, RIGHT ANGLE TWO PART BOARD CONNECTOR, SOLDER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 92909-102HLF | 功能描述:集管和線(xiàn)殼 RoHS:否 產(chǎn)品種類(lèi):1.0MM Rectangular Connectors 產(chǎn)品類(lèi)型:Headers - Pin Strip 系列:DF50 觸點(diǎn)類(lèi)型:Pin (Male) 節(jié)距:1 mm 位置/觸點(diǎn)數(shù)量:16 排數(shù):1 安裝風(fēng)格:SMD/SMT 安裝角:Right 端接類(lèi)型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Gold 制造商:Hirose Connector |

| 92909-103HLF | 功能描述:集管和線(xiàn)殼 RoHS:否 產(chǎn)品種類(lèi):1.0MM Rectangular Connectors 產(chǎn)品類(lèi)型:Headers - Pin Strip 系列:DF50 觸點(diǎn)類(lèi)型:Pin (Male) 節(jié)距:1 mm 位置/觸點(diǎn)數(shù)量:16 排數(shù):1 安裝風(fēng)格:SMD/SMT 安裝角:Right 端接類(lèi)型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Gold 制造商:Hirose Connector |

| 92909-104HLF | 功能描述:集管和線(xiàn)殼 RoHS:否 產(chǎn)品種類(lèi):1.0MM Rectangular Connectors 產(chǎn)品類(lèi)型:Headers - Pin Strip 系列:DF50 觸點(diǎn)類(lèi)型:Pin (Male) 節(jié)距:1 mm 位置/觸點(diǎn)數(shù)量:16 排數(shù):1 安裝風(fēng)格:SMD/SMT 安裝角:Right 端接類(lèi)型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Gold 制造商:Hirose Connector |

| 92909-105HLF | 功能描述:集管和線(xiàn)殼 RoHS:否 產(chǎn)品種類(lèi):1.0MM Rectangular Connectors 產(chǎn)品類(lèi)型:Headers - Pin Strip 系列:DF50 觸點(diǎn)類(lèi)型:Pin (Male) 節(jié)距:1 mm 位置/觸點(diǎn)數(shù)量:16 排數(shù):1 安裝風(fēng)格:SMD/SMT 安裝角:Right 端接類(lèi)型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Gold 制造商:Hirose Connector |

| 92909-106HLF | 功能描述:集管和線(xiàn)殼 RoHS:否 產(chǎn)品種類(lèi):1.0MM Rectangular Connectors 產(chǎn)品類(lèi)型:Headers - Pin Strip 系列:DF50 觸點(diǎn)類(lèi)型:Pin (Male) 節(jié)距:1 mm 位置/觸點(diǎn)數(shù)量:16 排數(shù):1 安裝風(fēng)格:SMD/SMT 安裝角:Right 端接類(lèi)型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Gold 制造商:Hirose Connector |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。