- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98080 > SII3124ACBHU PCI BUS CONTROLLER, PBGA364 PDF資料下載

參數(shù)資料

| 型號: | SII3124ACBHU |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA364 |

| 封裝: | 21 X 21 MM, 1 MM PITCH, GREEN, BGA-364 |

| 文件頁數(shù): | 29/88頁 |

| 文件大小: | 592K |

| 代理商: | SII3124ACBHU |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

PCI-X to Serial ATA Controller

Data Sheet

Silicon Image, Inc.

2006 Silicon Image, Inc.

SiI-DS-0160-C

35

5.3.8

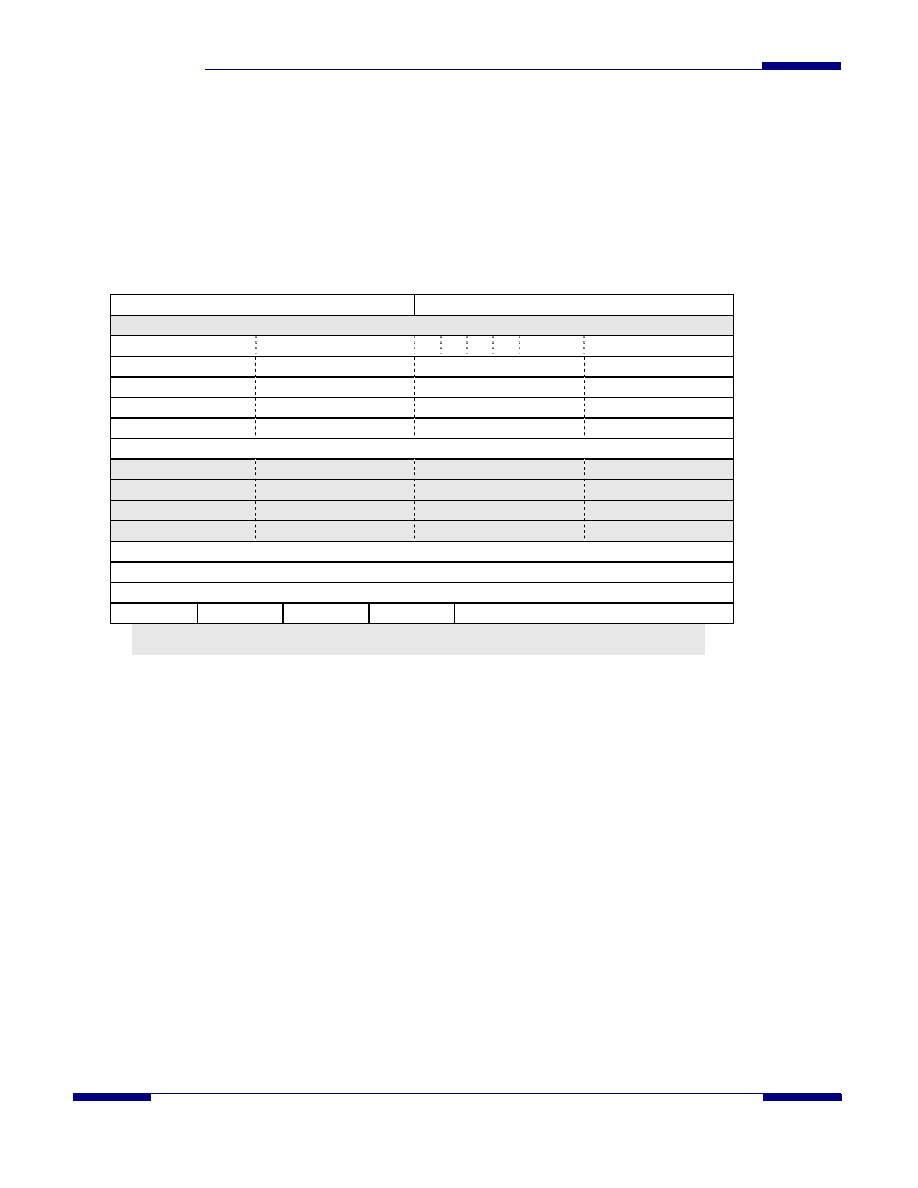

PACKET Command PRB Structure

Table 5-7 shows the layout for PACKET commands. The Control and protocol override fields must be populated as described

above. The PACKET PRB FIS area is structured the same as a standard ATA command. The FIS area contains the PACKET

ATA command. After the initial PACKET command is transmitted, the device will respond with a “PIO Setup” FIS, requesting a

12 or 16-byte ATAPI command. The host driver must populate the area normally used for the first SGE with the desired

ATAPI command. The length of the ATAPI command is determined by the value of the packet length bit (Port Control, bit 5).

If packet length is 0, 12 bytes will be transmitted. If packet length is one, 16 bytes will be transmitted. The packet length field

must be initialized with the packet length value returned by the device in the IDENTIFY PACKET command. Table 5-7 shows

a representative 12-byte ATAPI command layout.

31

0

Protocol Override

Control

0x00

Received Transfer Count

0x04

Features / Error

Command / Status

C

R

PMP

FIS Type

0x08

Dev/Head

Cyl High

Cyl Low

Sector Number

0x0C

Features (Exp)

Cyl High (Exp)

Cyl Low (Exp)

Sector Num (Exp)

0x10

Device Control

Reserved

Sector Count (Exp)

Sector Count

0x14

Reserved

0x18

Reserved – Must Be Zero

0x1C

LBA

LBA (MSB)

Reserved

ATAPI opcode

0x20

XFR Length (MSB)

Reserved

LBA (LSB)

LBA

0x24

Reserved

XFR Length (LSB)

0x28

Reserved

0x2C

SGE1 Data Address Low

0x30

SGE1 Data Address High

0x34

SGE1Data Count

0x38

SGE1 TRM

SGE1 LNK

SGE1 DRD

SGE1 XCF

Reserved[27:0]

0x3C

*Highlighted ATAPI packet is an example typical of some commands; other command packets

will have different formats within the highlighted bytes.

Table 5-7 Port Request Block For PACKET Command

The SiI3124 does not decode the ATAPI command to determine the necessity or direction of any associated data transfer.

The host driver must supply this information by setting control_packet_read (control field, bit4) or control_packet_write (control

field, bit 5) for any PACKET command that requires data transfer. Failure to set one of these bits for an ATAPI command that

requests data transfer will result in an Overrun or Underrun Command Error condition.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SII3512ECTU128 | PCI BUS CONTROLLER, PQFP128 |

| SII3531ACNU | PCI BUS CONTROLLER, QCC48 |

| SIO10N268-NU | MULTIFUNCTION PERIPHERAL, PQFP128 |

| SIS300 | GRAPHICS PROCESSOR, PBGA365 |

| SK12430PJT | 800 MHz, OTHER CLOCK GENERATOR, PQCC28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SII3132 | 制造商:SILICONIMAGE 制造商全稱:SILICONIMAGE 功能描述:PCI Express to 2-Port Serial ATA II Host Controller |

| SII3132CNU | 制造商:Silicon Image Inc 功能描述:PCI Express to Serial ATA Controller 88-Pin QFN |

| SII3512 | 制造商:SILICONIMAGE 制造商全稱:SILICONIMAGE 功能描述:PCI to Serial ATA Controller |

| SII3512ECTU128 | 制造商:Silicon Image Inc 功能描述:PCI to Serial ATA Controller 128-Pin TQFP 制造商:Silicone Image 功能描述: |

| SII3531 | 制造商:SILICONIMAGE 制造商全稱:SILICONIMAGE 功能描述:SteelVine⑩ Host Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復。