- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98080 > SII3124ACBHU PCI BUS CONTROLLER, PBGA364 PDF資料下載

參數(shù)資料

| 型號(hào): | SII3124ACBHU |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA364 |

| 封裝: | 21 X 21 MM, 1 MM PITCH, GREEN, BGA-364 |

| 文件頁數(shù): | 10/88頁 |

| 文件大?。?/td> | 592K |

| 代理商: | SII3124ACBHU |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

PCI-X to Serial ATA Controller

Data Sheet

Silicon Image, Inc.

2006 Silicon Image, Inc.

SiI-DS-0160-C

18

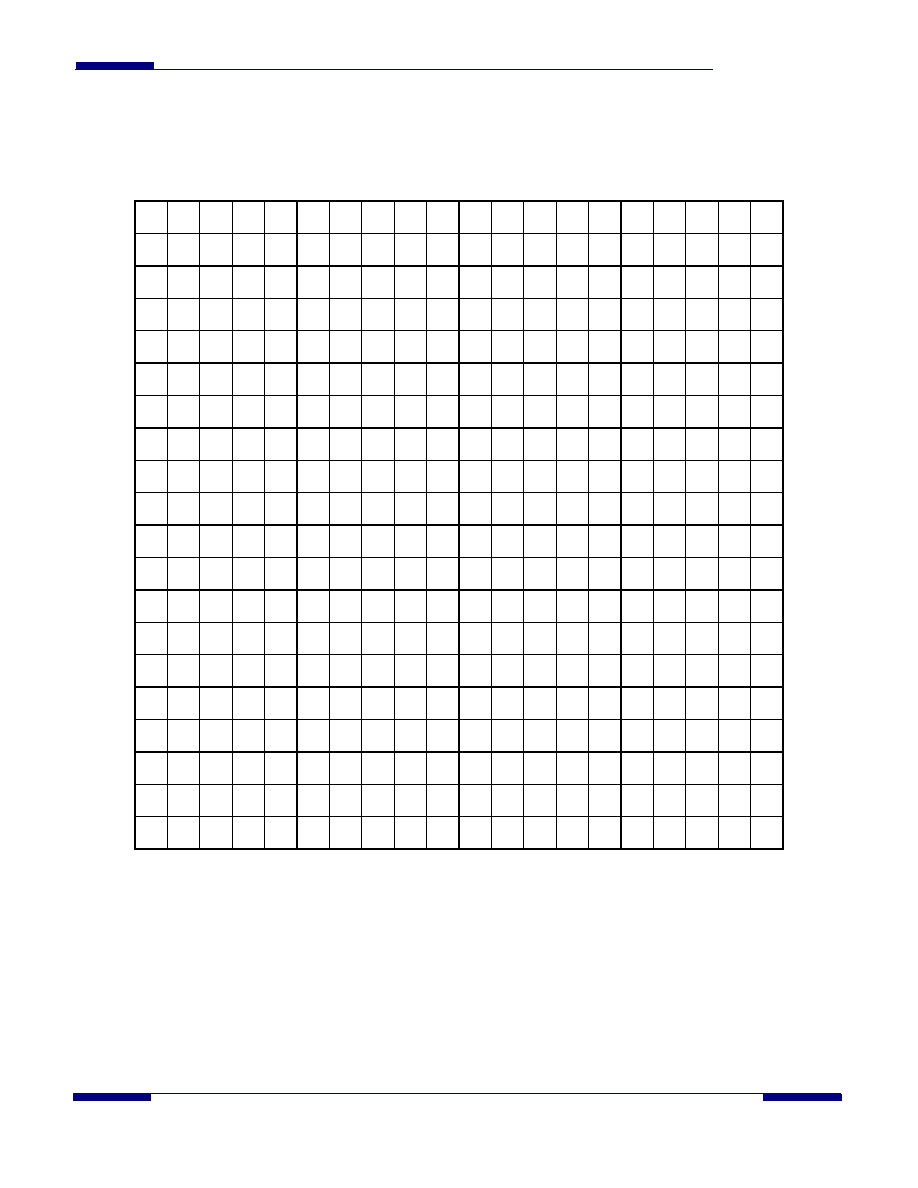

3.2 SiI3124 Ball Mapping

The diagram below shows the ball mapping for the SiI3124. Some signal names have been abbreviated to fit.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

A

N/C

PHY

TESTC

FL_

RD

FL_

AD16

FL_

AD13

FL_

AD10

FL_

AD7

FL_

AD4

FL_

AD1

FL_DA

TA6

FL_DA

TA3

FL_DA

TA0

P_

AD33

P_

AD35

P_

AD37

P_

AD39

VSS

D

A

B

VSS

A

VSS

A

VSS

A

VSS

A

I2C_

SCLK

FL_

WR

FL_

AD17

FL_

AD14

FL_

AD11

FL_

AD8

FL_

AD5

FL_

AD2

FL_DA

TA7

FL_DA

TA4

FL_DA

TA1

P_

AD34

P_

AD36

P_

AD38

VSS

D

P_

AD41

B

C

RX3+

RX3-

VDD

RX23

PHY

TESTD

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

P_

AD42

P_

AD43

C

D

TX3-

TX3+

VSS

A

VSS

A

I2C_

SDAT

FL_

CS

FL_

AD18

FL_

AD15

FL_

AD12

FL_

AD9

FL_

AD6

FL_

AD3

FL_

AD0

FL_DA

TA5

FL_DA

TA2

P_

AD32

P_

AD40

VSS

D

P_

AD44

P_

AD45

D

E

VDD

RX23

VSS

A

VDD

RX23

VSS

A

VSS

A

NC

VDD

O

VDD

O

VDD

O

VDD

D

VDD

D

VDD

D

VDD

D

VDD

D

VDD

D

P_

AD46

VSS

D

P_

AD48

P_

AD47

E

F

RX2+

RX2-

VSS

A

VDD

RX23

VSS

A

VDD

D

P_

AD50

VSS

D

P_

AD49

P_

AD51

F

G

TX2-

TX2+

VDD

TX23

VSS

A

VSS

A

VSS

A

VSS

A

VSS

A

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VDD

O

P_

AD52

VSS

D

P_

AD54

P_

AD53

G

H

VSS

A

VDD

TX23

VSS

A

VDD

TX23

VSS

A

VSS

A

VSS

A

VSS

A

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VDD

O

P_

AD56

VSS

D

P_

AD55

P_

AD57

H

J

XTALI XTALO

VDD

PLLA

REXT

VSS

A

VSS

A

VSS

A

VSS

A

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VDD

O

P_

AD58

VSS

D

P_

AD60

P_

AD59

J

K

VSS

A

VDD

PLLA

VSS

A

VSS

A

VSS

A

VSS

A

VSS

A

VSS

A

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VDD

O

P_

AD62

VSS

D

P_

AD61

P_

AD63

K

L

RX1+

RX1-

VDD

RX01

VSS

A

VSS

A

VSS

A

VSS

A

VSS

A

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VDD

O

P_

PAR64

VSS

D

P_CBE

N5

P_CBE

N4

L

M

TX1-

TX1+

VSS

A

VDD

RX01

VSS

A

VSS

A

VSS

A

VSS

A

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VDD

O

P_

REQ64

VSS

D

P_CBE

N7

P_CBE

N6

M

N

VDD

RX01

VSS

A

VDD

RX01

VSS

A

VSS

A

VSS

A

VSS

A

VSS

A

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VDD

O

P_

AD0

VSS

D

P_

ACK64

P_

AD1

N

P

RX0+

RX0-

VSS

A

VDD

TX01

VSS

A

VSS

A

VSS

A

VSS

A

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VDD

O

P_

AD2

VSS

D

P_

AD4

P_

AD3

P

R

TX0-

TX0+

VDD

TX01

VSS

A

VSS

A

VDD

D

P_

AD6

VSS

D

P_

AD5

P_

AD7

R

T

VSS

A

VDD

TX01

VSS

A

VSS

A

VSS

A

VDD

O

VDD

O

VDD

O

VDD

O

VDD

O

VDD

O

VDD

D

VDD

D

VDD

D

VDD

D

VDD

D

P_CBE

N0

VSS

D

P_

AD8

M66EN

T

U

P_

CLK

VSS

PLLB

VDD

PLLB

VSS

PLLB

VSS

PLLB

P_

RST#

P_

GNT#

P_

AD30

P_

AD26

P_

AD24

P_

AD22

P_

AD20

P_

AD16

P_FRA

ME#

P_

STOP

P_

TRDY

P_

AD15

VSS

D

P_

AD9

P_

AD10

U

V

VSS

PLLB

VDD

PLLB

VSS

PLLB

TDI

P_

INTA#

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

VSS

D

P_

AD11

P_

AD12

V

W

LED3

LED2 TRSTN TMS

P_

INTB#

P_

INTC#

VSS

D

P_

AD29

P_

AD28

P_CBE

N3

P_

IDSEL

P_

AD19

P_

AD18

P_

IRDY

P_DEV

SEL

P_

PERR#

P_

PAR

P_

AD13

VSS

D

VSS

D

W

Y

LED1

LED0

SCAN_

MODE

TCK

TDO

P_

INTD#

P_

REQ#

P_

AD31

P_

AD27

P_

AD25

P_

AD23

P_

AD21

P_

AD17

P_CBE

N2

P_

LOCK#

P_

SERR#

P_CBE

N1

P_

AD14

VSS

D

VSS

D

Y

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

Figure 3-1 Ball Mapping Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SII3512ECTU128 | PCI BUS CONTROLLER, PQFP128 |

| SII3531ACNU | PCI BUS CONTROLLER, QCC48 |

| SIO10N268-NU | MULTIFUNCTION PERIPHERAL, PQFP128 |

| SIS300 | GRAPHICS PROCESSOR, PBGA365 |

| SK12430PJT | 800 MHz, OTHER CLOCK GENERATOR, PQCC28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SII3132 | 制造商:SILICONIMAGE 制造商全稱:SILICONIMAGE 功能描述:PCI Express to 2-Port Serial ATA II Host Controller |

| SII3132CNU | 制造商:Silicon Image Inc 功能描述:PCI Express to Serial ATA Controller 88-Pin QFN |

| SII3512 | 制造商:SILICONIMAGE 制造商全稱:SILICONIMAGE 功能描述:PCI to Serial ATA Controller |

| SII3512ECTU128 | 制造商:Silicon Image Inc 功能描述:PCI to Serial ATA Controller 128-Pin TQFP 制造商:Silicone Image 功能描述: |

| SII3531 | 制造商:SILICONIMAGE 制造商全稱:SILICONIMAGE 功能描述:SteelVine⑩ Host Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。