- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98068 > S1C88104P0A0100 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, PBGA240 PDF資料下載

參數(shù)資料

| 型號: | S1C88104P0A0100 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, PBGA240 |

| 封裝: | VFBGA10H-216 |

| 文件頁數(shù): | 147/211頁 |

| 文件大小: | 1802K |

| 代理商: | S1C88104P0A0100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁當(dāng)前第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁

32

EPSON

S1C8F626 TECHNICAL MANUAL

5 PERIPHERAL CIRCUITS AND THEIR OPERATION (Watchdog Timer)

5.3.3 Control of watchdog timer

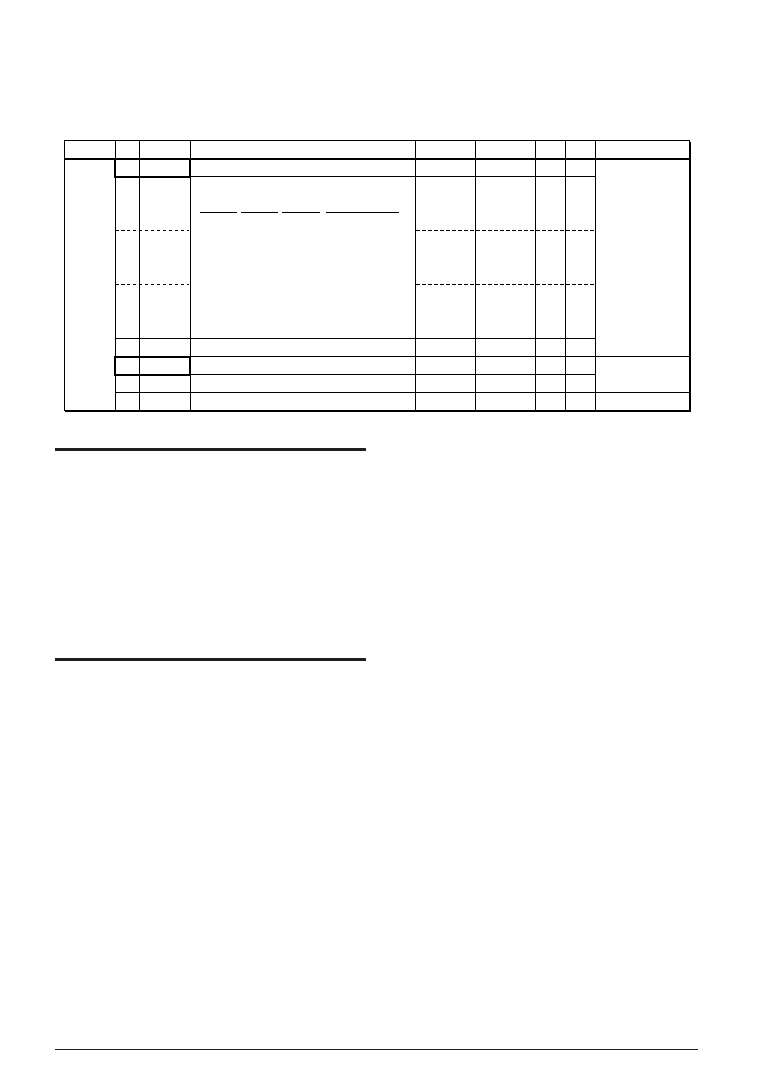

Table 5.3.3.1 shows the control bits for the watchdog timer.

Table 5.3.3.1 Watchdog timer control bits

SR R/W

Address Bit

Name

Function

Comment

10

00FF40 D7

D6

D5

D4

D3

D2

D1

D0

WDEN

FOUT2

FOUT1

FOUT0

WDRST

TMRST

TMRUN

Constantly "0" when

being read

1

0

–

0

R/W

W

R/W

Enable

On

Reset

Run

Disable

Off

No operation

Stop

Watchdog timer enable

FOUT frequency selection

FOUT output control

Watchdog timer reset

Clock timer reset

Clock timer Run/Stop control

FOUTON

FOUT2

1

0

FOUT1

1

0

1

0

FOUT0

1

0

1

0

1

0

1

0

Frequency

fOSC3 / 8

fOSC3 / 4

fOSC3 / 2

fOSC3 / 1

fOSC1 / 8

fOSC1 / 4

fOSC1 / 2

fOSC1 / 1

WDEN: 00FF40HD7

Selects whether the watchdog timer is used

(enabled) or not (disabled).

When "1" is written: Enabled

When "0" is written: Disabled

Reading:

Valid

When "1" is written to the WDEN register, the

watchdog timer starts count operation. When "0" is

written, the watchdog timer does not count and

_______

does not generate the interrupt (NMI).

At initial reset, this register is set to "1".

WDRST: 00FF40HD2

Resets the watchdog timer.

When "1" is written: Watchdog timer is reset

When "0" is written: No operation

Reading:

Constantly "0"

By writing "1" to WDRST, the watchdog timer is

reset, after which it is immediately restarted.

Writing "0" will mean no operation.

Since WDRST is for writing only, it is constantly set

to "0" during readout.

5.3.4 Programming notes

(1) When the watchdog timer is being used, the

software must reset it within 4-second cycles

(when fOSC1 is 32.768 kHz).

(2) Do not execute the SLP instruction for 2 msec

_______

after a NMI interrupt has occurred (when fOSC1

is 32.768 kHz).

(3) Because the watchdog timer is set in operation

state by initial reset, set the watchdog timer to

disabled state (not used) before generating an

_______

interrupt (NMI) if it is not used.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1C88317D0A0100 | MICROCONTROLLER, UUC170 |

| S1C88308D0A0100 | MICROCONTROLLER, UUC170 |

| S1C88308F0A0100 | MICROCONTROLLER, PQFP160 |

| S1C88348F | 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, PQFP16 |

| S1C88316D | 8-BIT, MROM, 8.2 MHz, MICROCONTROLLER, UUC172 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1C88349 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88649 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88650 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88655 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

| S1C88816 | 制造商:EPSON 制造商全稱:EPSON 功能描述:8-bit Single Chip Microcomputer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。