- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98011 > MC68838FCC (MOTOROLA INC) 1 CHANNEL(S), 125M bps, FDDI CONTROLLER, CQFP120 PDF資料下載

參數(shù)資料

| 型號: | MC68838FCC |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1 CHANNEL(S), 125M bps, FDDI CONTROLLER, CQFP120 |

| 封裝: | CERAMIC, QFP-120 |

| 文件頁數(shù): | 60/100頁 |

| 文件大?。?/td> | 465K |

| 代理商: | MC68838FCC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當(dāng)前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

MOTOROLA

MC68838 USER’S MANUAL

5-3

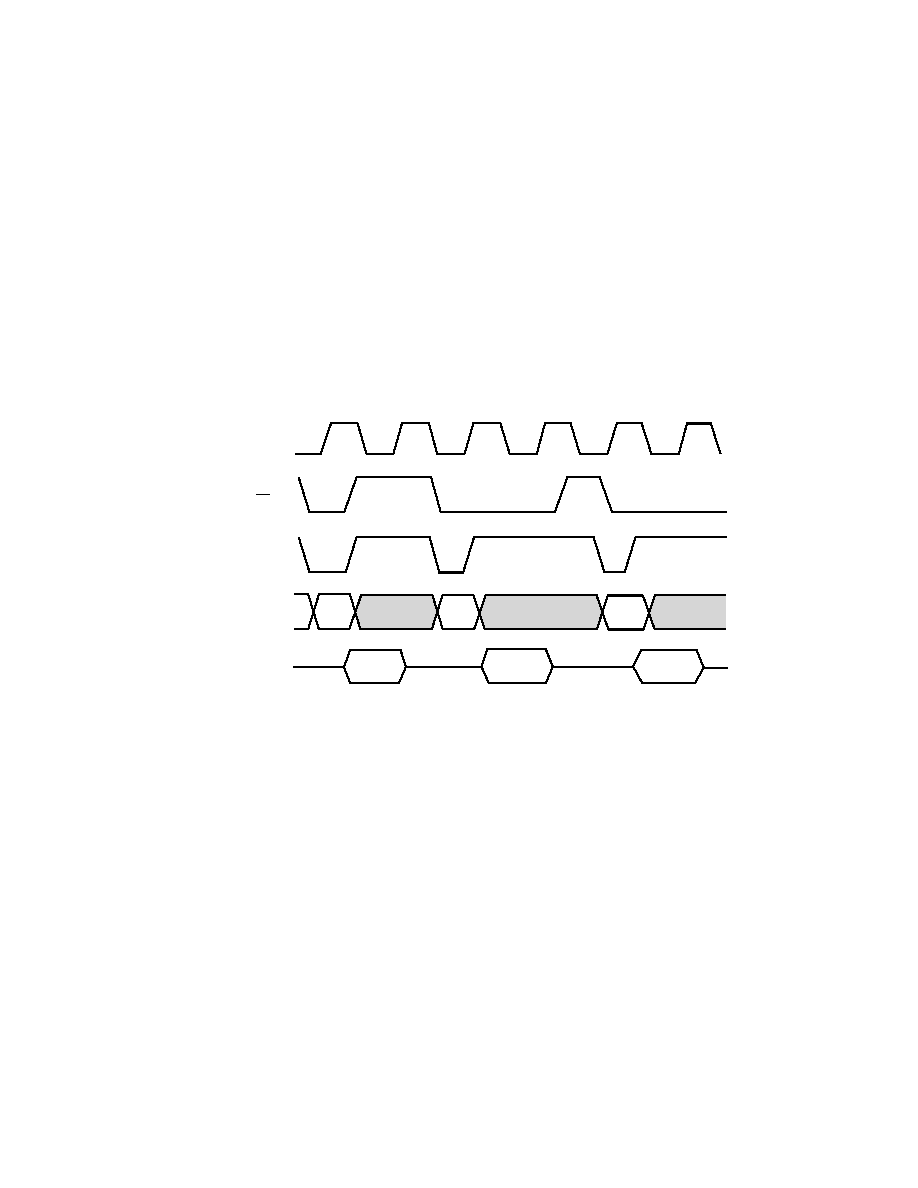

5.3 WRITE CYCLE

The NP uses a write cycle to write data into a MAC register (see Figure 5-2). It is similar

to the read cycle previously described. The principal differences are as follows:

1. The NPRW line must be low a setup time before, and a hold time after, the first

rising edge of NPCLK after

MACSEL is asserted, and

2. The data to be written must be valid a setup time before, and a hold time after, the

second rising edge of NPCLK after

MACSEL is asserted.

The host bus logic can assert

MACSEL to introduce as many wait states as necessary.

Like the MAC, the NP must three-state the NPDx bus within 40 ns after the second rising

edge of NPCLK after

MACSEL is negated. Thus, by delaying the negation of MACSEL,

the NP can extend the time it has to three-state the NPDx bus. The negation of

MACSEL

has no effect on the MAC in a write cycle. See 5.2 Read Cycle for more details.

NPD

CS

NPRW

NPA

BYTCLK (NPCLK)

Figure 5-2. Node Processor Bus Write Cycles

ARCHIVE

INFORMA

TION

ARCHIVE

INFORMA

TION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68EC020FG | 32-BIT, 25 MHz, MICROCONTROLLER, PQFP100 |

| MC68HC05CC1P | 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PDIP40 |

| MC68HC05CC2B | 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PDIP42 |

| MC68HC05CT4FN | 8-BIT, MROM, 2.048 MHz, MICROCONTROLLER, PQCC44 |

| MC68HC05J1P | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PDIP20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68840FE25B | 制造商:Motorola Inc 功能描述:68840FE25B |

| MC68840FE-25B | 制造商:Motorola Inc 功能描述:68840FE-25B |

| MC6885 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HEX THREE-STATE BUFFER/INVERTERS |

| MC68851 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:32-Bit Paged Memory Management Unit |

| MC6885L | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HEX THREE-STATE BUFFER/INVERTERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。