- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382686 > TSB12LV01APZ (Texas Instruments, Inc.) High-Speed Serial-Bus Link-Layer Controller PDF資料下載

參數(shù)資料

| 型號: | TSB12LV01APZ |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | High-Speed Serial-Bus Link-Layer Controller |

| 中文描述: | 高速串行總線鏈路層控制器 |

| 文件頁數(shù): | 22/71頁 |

| 文件大小: | 267K |

| 代理商: | TSB12LV01APZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

3–4

Table 3–2.

Node-Address/Transmitter Acknowledge Register Field Descriptions (Continued)

BITS

31

ACRONYM

FUNCTION NAME

DESCRIPTION

AckV

Acknowledge valid

Whenever an ack packet is received, AckValid is set to 1. After

the node-address/transmitter acknowledge register is read,

AckValid is automatically reset to 0. This bit is also used to

indicate abitration failure. If a non-broadcast asynchronous

packet is in the ATF ready to transmit and a TxRdy interrupt

occurs, and AckValid is 0, this indicates no ack packet was

received and no ack time-out occured. The packet is still in the

ATF and the TSB12LV01A automatically arbitrates for the bus

again. Under normal conditions AckValid=0 means ATAck

contains last received ack code information.

This bit is new to the TSB12LV01A and does not exist in the TSB12C01A.

3.2.3

The control register dictates the basic operation of the TSB12LV01A. This register is at address 08h and

is read/write. The initial value is 0000_0000h.

Control Register (@08h)

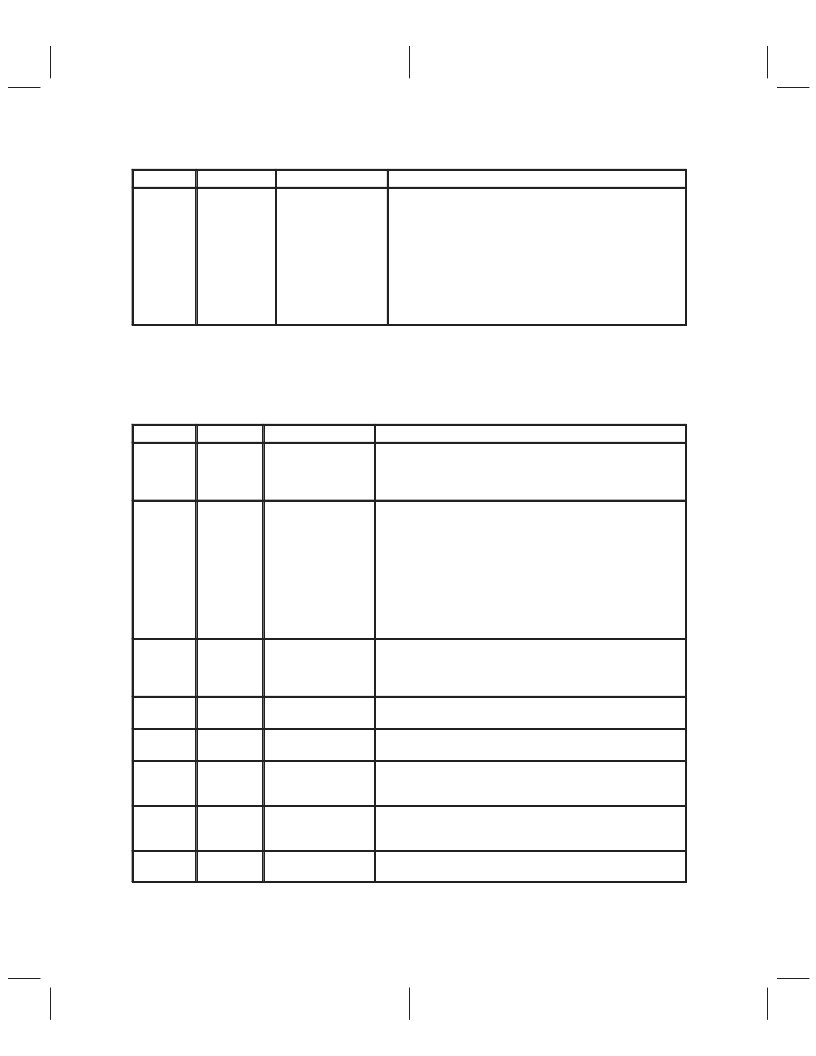

Table 3–3. Control-Register Field Descriptions

BITS

ACRONYM

FUNCTION NAME

DESCRIPTION

0

IdVal

ID valid

When IdVal is set, the TSB12LV01A accepts packets addressed

to the IEEE 1212 address set (Node Number) in the node-address

register. When IdVal is cleared, the TSB12LV01A accepts only

broadcast packets.

1

RxSId

Received self-ID

packets

When RxSId is set, the self-identification packets generated by

phy chips during bus initialization are received and placed into the

GRF as a single packet. Each self-identification packet is

composed of two quadlets, where the second quadlet is the logical

inverse of the first. If ACK (4 bits) equals 1h, then the data is good.

If ACK equals Dh, then the data is wrong. When the RxSld is set

to 1, it also receives and places Link-on-packet and PHY

Configuration packet into the GRF. For Link-on-packet and PHY

Configuration packet only the first quadlet of each packet is stored

in the GRF.

2

BsyCtrl

Busy control

When this bit is set, this node sends an ack_busy_x acknowledge

in response to all received non-broadcast asynchronous packets.

When this bit is clear, this node sends ack_busy_x acknowledge

only if the GRF is full.

3

RAI

Received all isochro-

nous packets

If RAI = 1 , RxIEn = 1, TSB12LV01A receives all Isochronous

packets and stores in the GRF.

4

RcvCySt

Receive cycle start

If RcvCySt = 1, it stores the received cycle start packet in the

GRF.

5

TxAEn

Transmitter enable

When TxAEn is cleared, the transmitter does not arbitrate or send

asynchronous packets. After bus reset, TxAEn is cleared since

the node number may have changed.

6

RxAEn

Receiver enable

When RxAEn is cleared, the receiver does not receive any

asynchronous packets. After bus reset, RxAEn is cleared since

the node number may have changed.

7

TxIEn

Transmit

isochronous enable

When TxIEn is cleared, the transmitter does not arbitrate to send

isochronous packets

This bit is new to the TSB12LV01A and does not exist in the TSB12C01A.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB3055 | IC APEX 20KE FPGA 300K 240-PQFP |

| TSB41AB3 | IC APEX 20KE FPGA 400K 672-FBGA |

| TSB41BA3-EP | IC APEX 20KE FPGA 400K 672-FBGA |

| TSB41LV03PFP | IC APEX 20KE FPGA 600K 652-BGA |

| TSB41AB2I | IEEE 1394a-2000 TWO-PORT CABLE TRANSCEVER/ARBITER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB12LV01B | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 HIGH SPEED SERIAL BUS LINK LAYER CONTROLLER |

| TSB12LV01B-EP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Military Enhanced Plastic High Performance 1394 3.3V Link Layer for Telecom. Embedded & Indust. App. |

| TSB12LV01BIPZT | 功能描述:1394 接口集成電路 High Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01BIPZTEP | 功能描述:1394 接口集成電路 Mil Enh Hi Perf 1394 3.3V Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB12LV01BPZ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:BUS CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。