- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98081 > SII3512ECTU128 PCI BUS CONTROLLER, PQFP128 PDF資料下載

參數(shù)資料

| 型號(hào): | SII3512ECTU128 |

| 元件分類(lèi): | 總線(xiàn)控制器 |

| 英文描述: | PCI BUS CONTROLLER, PQFP128 |

| 封裝: | LEAD FREE, TQFP-128 |

| 文件頁(yè)數(shù): | 65/132頁(yè) |

| 文件大?。?/td> | 3011K |

| 代理商: | SII3512ECTU128 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)當(dāng)前第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)

SiI3512 PCI to Serial ATA Controller

Data Sheet

Silicon Image, Inc.

30

2007-2010 Silicon Image, Inc. All rights reserved.

DS-0102-D01

CONFIDENTIAL

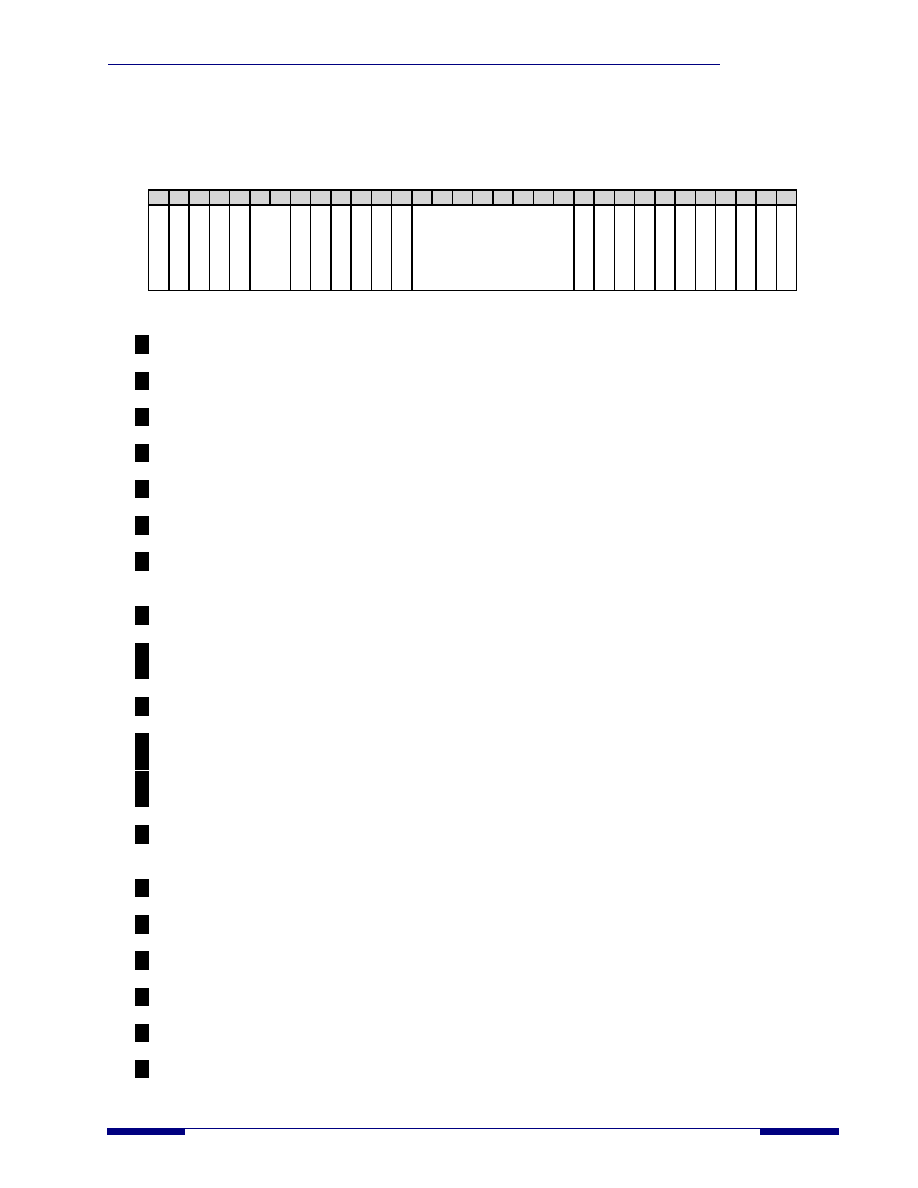

PCI Status – PCI Command

Address Offset: 0x04

Access Type: Read/Write/Write-One-to-Clear

Reset Value: 0x02B0_0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

De

t

P

ar

E

rr

S

ig

S

ys

E

rr

Rc

vd

M

Abort

Rc

vd

T

Abort

S

ig

T

Abort

De

vs

el

T

im

in

g

De

t

M

Dat

a

P

ar

E

rr

F

as

t

B

-to

-B

Capab

le

Re

se

rve

d

66

-M

Hz

Capab

le

Capab

il

it

ies

L

is

t

In

t

S

tat

u

s

Reserved

In

t

Dis

ab

le

F

as

t

B

-to

-B

E

n

ab

le

S

E

RR

E

n

ab

le

Add

re

ss

S

te

p

in

g

P

ar

E

rr

or

Re

sp

on

se

VGA

P

alet

te

M

em

or

y

Wr

&

In

v

S

p

ec

ial

Cyc

les

B

u

s

M

as

te

r

M

em

or

y

S

p

ac

e

IO

S

p

ac

e

This register defines the various control functions associated with the PCI bus. The register bits are defined below.

Bit 31: Det. Par Err (R/W1C) – Detected Parity Error. This bit set indicates that the SiI3512 device detected a

parity error on the PCI bus-address or data parity error-while responding as a PCI target.

Bit 30: Sig. Sys Err (R/W1C) – Signaled System Error. This bit set indicates that the SiI3512 controller signaled

SERR on the PCI bus.

Bit 29: Rcvd M Abort (R/W1C) – Received Master Abort. This bit set indicates that the SiI3512 controller

terminated a PCI bus operation with a Master Abort.

Bit 28: Rcvd T Abort (R/W1C) – Received Target Abort. This bit set indicates that the SiI3512 controller received

a Target Abort termination.

Bit 27: Sig. T Abort (R/W1C) – Signaled Target Abort. This bit set indicates that the SiI3512 controller

terminated a PCI bus operation with a Target Abort.

Bit [26:25]: Devsel Timing (R) – Device Select Timing. This bit field indicates the DEVSEL timing supported by

the SiI3512 device. The hardwired value is 0b01 for Medium decode timing.

Bit 24: Det M Data Par Err (R/W1C) – Detected Master Data Parity Error. This bit set indicates that the SiI3512

controller, as bus master, detected a parity error on the PCI bus. The parity error may be either reported by the

target device via PERR# on a write operation or by the SiI3512 controller on a read operation.

Bit 23: Fast B-to-B Capable (R) – Fast Back-to-Back Capable. This bit is hardwired to 1 to indicate that the

SiI3512 controller is Fast Back-to-Back capable as a PCI target.

Bit 22: Reserved (R).

Bit 21: 66-MHz Capable (R) – 66-MHz PCI Operation Capable. This bit is hardwired to 1 to indicate that the

SiI3512 device is 66-MHz capable.

Bit 20: Capabilities List (R) – PCI Capabilities List. This bit is hardwired to 1 to indicate that the SiI3512

controller has a PCI Power Management Capabilities register linked at offset 0x34.

Bit 19: Interrupt Status (R).

Bit [18:11]: Reserved (R) – This bit field is reserved and returns zeros on a read.

Bit 10: Interrupt Disable (R/W)

Bit 09: Fast B-to-B Enable (R) – Fast Back-to-Back Enable. This bit is hardwired to 0 to indicate that the SiI3512

controller does not support Fast Back-to-Back operations as bus master.

Bit 08: SERR Enable (R/W) – SERR Output Enable. This bit set enables the SiI3512 controller to drive the PCI

SERR# pin when it detects an address parity error. The Parity Error Response bit (06) must also be set to enable

SERR# reporting.

Bit 07: Address Stepping (R) – Address Stepping Enable. This bit is hardwired to 0 to indicate that the SiI3512

controller does not support Address Stepping.

Bit 06: Par Error Response (R/W) – Parity Error Response Enable. This bit set enables the SiI3512 controller to

respond to parity errors on the PCI bus. If this bit is cleared, the SiI3512 controller will ignore PCI parity errors.

Bit 05: VGA Palette (R) – VGA Palette Snoop Enable. This bit is hardwired to 0 to indicate that the SiI3512

controller does not support VGA Palette Snooping.

Bit 04: Mem Wr & Inv (R) – Memory Write and Invalidate Enable. This bit is hardwired to 0 to indicate that the

SiI3512 device does not support Memory Write and Invalidate.

Bit 03: Special Cycles (R) – Special Cycles Enable. This bit is hardwired to 0 to indicate that the SiI3512

controller does not respond to Special Cycles.

Bit 02: Bus Master (R/W) – Bus Master Enable. This bit set enables the SiI3512 device to act as PCI bus master.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SII3531ACNU | PCI BUS CONTROLLER, QCC48 |

| SIO10N268-NU | MULTIFUNCTION PERIPHERAL, PQFP128 |

| SIS300 | GRAPHICS PROCESSOR, PBGA365 |

| SK12430PJT | 800 MHz, OTHER CLOCK GENERATOR, PQCC28 |

| SK12439PJ | 800 MHz, OTHER CLOCK GENERATOR, PQCC28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SII3531 | 制造商:SILICONIMAGE 制造商全稱(chēng):SILICONIMAGE 功能描述:SteelVine⑩ Host Controller |

| SII3531A | 制造商:SILICONIMAGE 制造商全稱(chēng):SILICONIMAGE 功能描述:PCI Express to Serial ATA Controller |

| SII3531ACNU | 制造商:Silicon Image Inc 功能描述:PCI Express to Serial ATA Controller 48-Pin QFN EP |

| SII3611 | 制造商:SILICONIMAGE 制造商全稱(chēng):SILICONIMAGE 功能描述:SATALink Device Bridge |

| SII3611CT80-1.5 | 制造商:SILICON IMAGE 功能描述:3611CT80-1.5 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。