- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98068 > S1C63653F 4-BIT, FLASH, 4 MHz, MICROCONTROLLER, CQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | S1C63653F |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, FLASH, 4 MHz, MICROCONTROLLER, CQFP100 |

| 封裝: | CERAMIC, QFP15-100 |

| 文件頁(yè)數(shù): | 35/121頁(yè) |

| 文件大小: | 1127K |

| 代理商: | S1C63653F |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)

12

EPSON

S1C63653 TECHNICAL MANUAL

CHAPTER 2: POWER SUPPLY AND INITIAL RESET

2.2 Initial Reset

To initialize the S1C63653 circuits, initial reset must be executed. There are two ways of doing this.

(1) External initial reset by the RESET terminal

(2) External initial reset by simultaneous high input to terminals K00–K03 (mask option setting)

The circuits are initialized by either (1) or (2). When the power is turned on, be sure to initialize using the

reset function. It is not guaranteed that the circuits are initialized by only turning the power on.

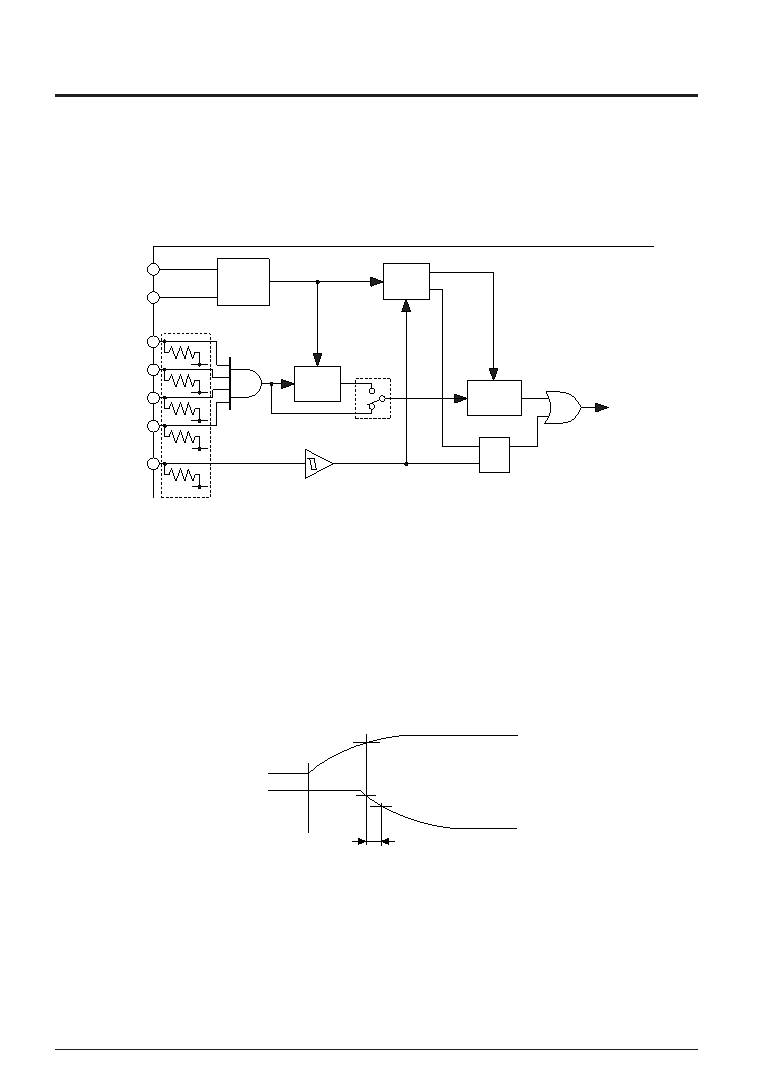

Figure 2.2.1 shows the configuration of the initial reset circuit.

RESET

K00

K01

K02

K03

OSC2

OSC1

oscillation

circuit

Noise

reject

circuit

RQ

S

Internal

initial

reset

Time

authorize

circuit

Divider

Mask option

1 Hz

2 Hz

VSS

Mask option

Fig. 2.2.1 Configuration of initial reset circuit

2.2.1 Reset terminal (RESET)

Initial reset can be executed externally by setting the reset terminal to a high level (VDD). After that the

initial reset is released by setting the reset terminal to a low level (VSS) and the CPU starts operation.

The reset input signal is maintained by the RS latch and becomes the internal initial reset signal. The RS

latch is designed to be released by a 2 Hz signal (high) that is divided by the OSC1 clock. Therefore in

normal operation, a maximum of 250 msec (when fOSC1 = 32.768 kHz) is needed until the internal initial

reset is released after the reset terminal goes to low level. Be sure to maintain a reset input of 0.1 msec or

more. However, when turning the power on, the reset terminal should be set at a high level as in the

timing shown in Figure 2.2.1.1.

Note that a reset pulse shorter than 100 nsec is rejected as noise.

VDD

RESET

2.0 msec or more

1.8 V

0.5VDD

0.9VDD or more (high level)

Power on

Fig. 2.2.1.1 Initial reset at power on

The reset terminal should be set to 0.9VDD or more (high level) until the supply voltage becomes 1.8 V

or more.

After that, a level of 0.5VDD or more should be maintained more than 2.0 msec.

The internal pull-down resistor of the RESET terminal can be enabled or disabled by mask option.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S1C6F567D0A0100 | MICROCONTROLLER, UUC141 |

| S1C6N3B0D0A0100 | MICROCONTROLLER, UUC54 |

| S1C6P366D0A0100 | 4-BIT, FLASH, 4.1 MHz, MICROCONTROLLER, UUC102 |

| S1C6P466D0A0A00 | MICROCONTROLLER, UUC140 |

| S1C6S2L7D | 4-BIT, MROM, 0.032 MHz, MICROCONTROLLER, UUC58 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S1C63656 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63657 | 制造商:EPSON 制造商全稱:EPSON 功能描述:CMOS 4-bit Single Chip Microcontroller |

| S1C63658 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63666 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

| S1C63709 | 制造商:EPSON 制造商全稱:EPSON 功能描述:4-bit Single Chip Microcomputer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。