- 您現在的位置:買賣IC網 > PDF目錄373065 > K4N56163QF-GC (SAMSUNG SEMICONDUCTOR CO. LTD.) 256Mbit gDDR2 SDRAM PDF資料下載

參數資料

| 型號: | K4N56163QF-GC |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256Mbit gDDR2 SDRAM |

| 中文描述: | 片256Mbit GDDR2 SDRAM的 |

| 文件頁數: | 17/73頁 |

| 文件大小: | 1262K |

| 代理商: | K4N56163QF-GC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

- 17 -

Rev 1.6 (Apr. 2005)

256M gDDR2 SDRAM

K4N56163QF-GC

7. All voltages are referenced to VSS.

8. Tests for AC timing, IDD, and electrical (AC and DC) characteristics, may be conducted at nominal reference/supply voltage levels,

but the related specifications and device operation are guaranteed for the full voltage range specified.

Specific Notes for dedicated AC parameters

9. User can choose which active power down exit timing to use via MRS(bit 12). tXARD is expected to be used for fast active power

down exit timing. tXARDS is expected to be used for slow active power down exit timing.

10. AL = Additive Latency

11. This is a minimum requirement. Minimum read to precharge timing is AL + BL/2 providing the tRTP and tRAS(min) have been

satisfied.

12. A minimum of two clocks (2 * tCK) is required irrespective of operating frequency

13. Timings are guaranteed with command/address input slew rate of 1.0 V/ns.

14. These parameters guarantee device behavior, but they are not necessarily tested on each device. They may be guaranteed by

device design or tester correlation.

15. Timings are guaranteed with data, mask, and (DQS in singled ended mode) input slew rate of 1.0 V/ns.

16. Timings are guaranteed with CK/CK differential slew rate of 2.0 V/ns. Timings are guaranteed for DQS signals with a differential

slew rate of 2.0 V/ns in differential strobe mode and a slew rate of 1V/ns in single ended mode.

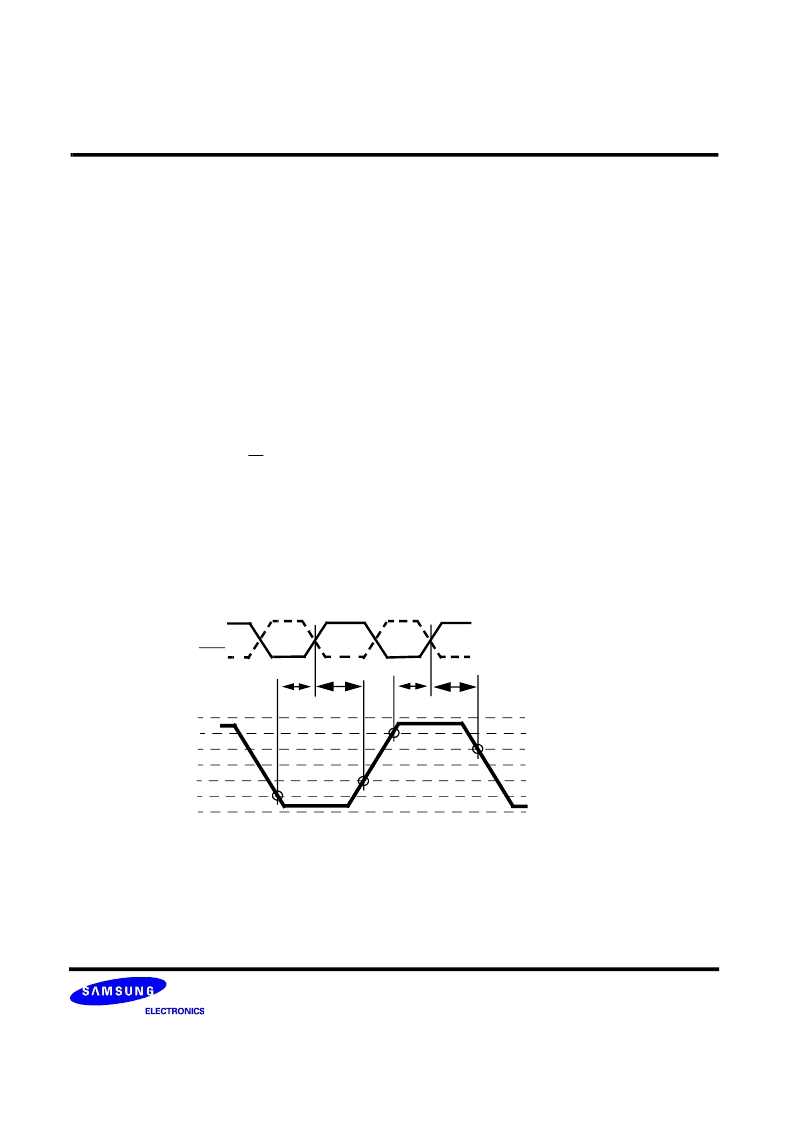

17. tDS and tDH (data setup and hold) derating

1) Input waveform timing is referenced from the input signal crossing at the V

IH

(AC) level for a rising signal and V

IL

(AC) for a

falling signal applied to the device under test.

2) Input waveform timing is referenced from the input signal crossing at the V

IH

(DC) level for a rising signal and V

IL

(DC) for a

falling signal applied to the device under test.

tDS

V

DDQ

V

IH

(AC) min

V

IH

(DC) min

V

REF

V

IL

(DC) max

V

IL

(AC) max

V

SS

DQS

DQS

tDH

tDS

tDH

<Data setup/hold timing>

相關PDF資料 |

PDF描述 |

|---|---|

| K4N56163QF-GC25 | 256Mbit gDDR2 SDRAM |

| K4N56163QF-GC30 | 256Mbit gDDR2 SDRAM |

| K4N56163QF-GC37 | 256Mbit gDDR2 SDRAM |

| K4PE68A | Transient Voltage Suppressor Diodes |

| K4R271669A | 256K x 16/18 bit x 2*16 Dependent Banks Direct RDRAMTM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| K4N56163QF-GC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit gDDR2 SDRAM |

| K4N56163QF-GC30 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit gDDR2 SDRAM |

| K4N56163QF-GC37 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:256Mbit gDDR2 SDRAM |

| K4N56163QG-ZC2A | 制造商:Samsung Semiconductor 功能描述: |

| K4P24V3 | 制造商:AROMAT 功能描述:REPLAY 700 OHM |

發(fā)布緊急采購,3分鐘左右您將得到回復。