- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1024 Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) PDF資料下載

參數(shù)資料

| 型號(hào): | HDMP-1024 |

| 英文描述: | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) |

| 中文描述: | 低成本千兆速率接收芯片組配備TTL的I / O(帶的TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) |

| 文件頁(yè)數(shù): | 31/40頁(yè) |

| 文件大小: | 363K |

| 代理商: | HDMP-1024 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

31

during the bit-slipping that occurs

in the initial frequency acquisition

of both the Tx and Rx PLLs.

When the local port is in State 0,

it is in the reset state, where both

local Tx and Rx parallel interfaces

are disabled. The local Tx trans-

mits FF0 continuously, and the

local Rx PLL is in the frequency

detection mode. When the local

Rx is phase-locked to the remote

Tx, it transitions to State 1. The

local Tx transmits FF1 to

acknowledge the phase-locked

condition (its parallel input is still

disabled). The local Rx PLL is in

the phase detection mode and its

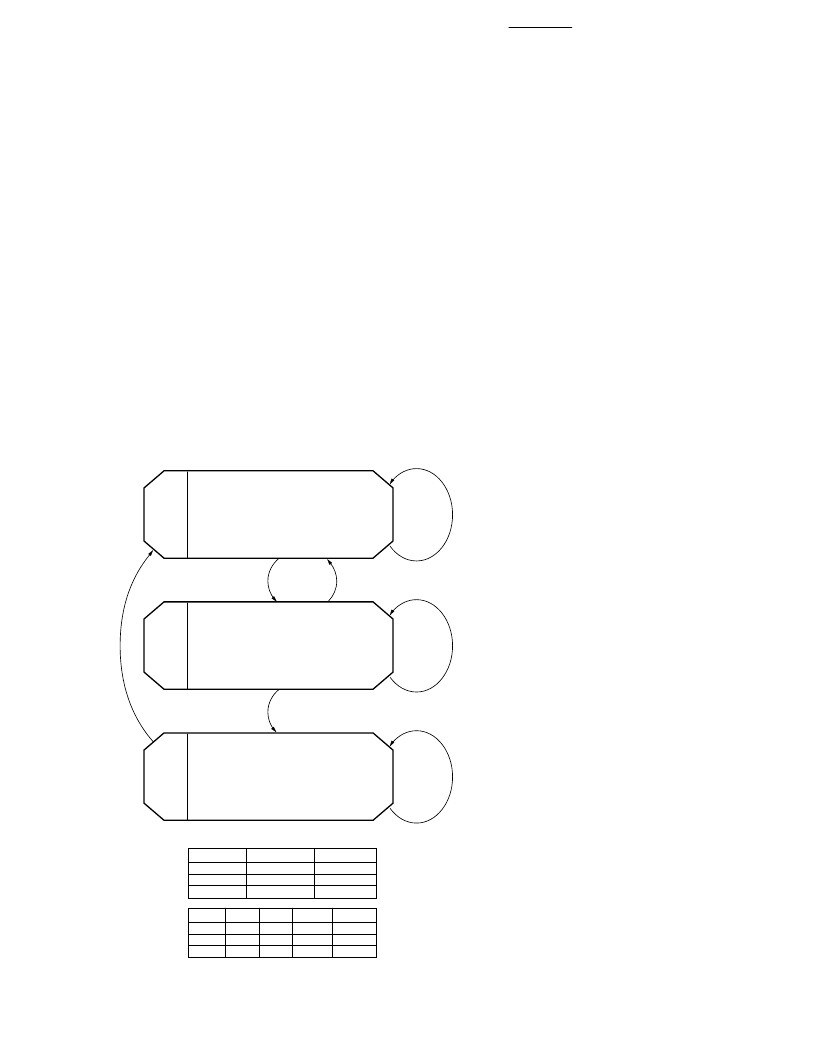

Figure 15 shows the state

diagram of the SMC. The SMC is

debounced by allowing state

transitions to be made only after

at least two consecutive frames

give the same indication. This

prevents single bit errors from

causing false state transitions. In

addition to this debouncing

mechanism, when two

consecutive ERROR or Resets

occur, a timer is enabled forcing

the SMC into state zero for 128

frame times. Any transition out of

this initial state can only occur

after the link has been error-free

for 128 frames. This prevents

false transitions from being made

parallel output is enabled. When

in State 2, the two-way synchroni-

zation between the local port and

the remote port is established.

Both local Tx and Rx parallel

interfaces are enabled, and the

local Rx PLL is in the phase detec-

tion mode. Parallel data can be

sent by the local Tx, and at the

same time, received by the local

Rx.

The Rx chip has the state machine

logic built in. The SMC has two

status outputs, STAT0 and STAT1,

that control the various features

of the two chips depending on the

current state. The TX inputs that

need to be controlled are FF and

ED. The Rx inputs that need to be

controlled are FDIS and ACTIVE.

To control the chips as shown in

the state diagram of Figure 15,

the following interchip

connections must be made

(Figure 16):

Tx FF is driven by STAT1

Tx ED is driven by STAT0

Rx FDIS is driven by STAT1

Rx ACTIVE is driven by STAT1

Tx RST* and Rx SMRST0* are

driven by a power-on, or user,

reset circuit.

Figure 15. HDMP-1024 (Rx) State Machine State Diagram.

SEND FF0

DISABLE DATA TRANSMISSION

DISABLE DATA RECEPTION

FREQUENCY DETECTOR ON

0

DATA

ERROR

RESET

SEND FF1

DISABLE DATA TRANSMISSION

ENABLE DATA RECEPTION

FREQUENCY DETECTOR OFF

1

FF0

SEND FF0

ENABLE DATA TRANSMISSION

ENABLE DATA RECEPTION

FREQUENCY DETECTOR OFF

2

DATA

FF1

FF1

FF0

ERROR

RESET

DATA

FF1

FF0

ERROR

RESET

STATE

STAT1 PIN

STAT0 PIN

0

0

1

0

1

2

0

1

1

STATE

0

1

2

Tx FF

0

1

1

Tx ED

0

0

1

Rx FDIS Rx ACTIVE

0

1

1

0

1

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

| HDMP-1514 | Fibre Channel Receiver Chipset(光纖通道接收芯片) |

| HDMP-1526 | Transistor Diode Kit;Contents Of Kit:Transistor/Diode Kit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034A | 制造商:HP 制造商全稱:Agilent(Hewlett-Packard) 功能描述:Transmitter/Receiver Chip Set |

| HDMP-1512 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Fibre Channel Transmitter and Receiver Chipset |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。