- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄15530 > EVAL-ADUC7023QSPZ1 (Analog Devices Inc)BOARD EVAL FOR ADUC7023 PDF資料下載

參數(shù)資料

| 型號(hào): | EVAL-ADUC7023QSPZ1 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 61/96頁 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADUC7023 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 類型: | MCU |

| 適用于相關(guān)產(chǎn)品: | ADuC7023 |

| 所含物品: | 板 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當(dāng)前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

ADuC7023

Data Sheet

| Page 64 of 96

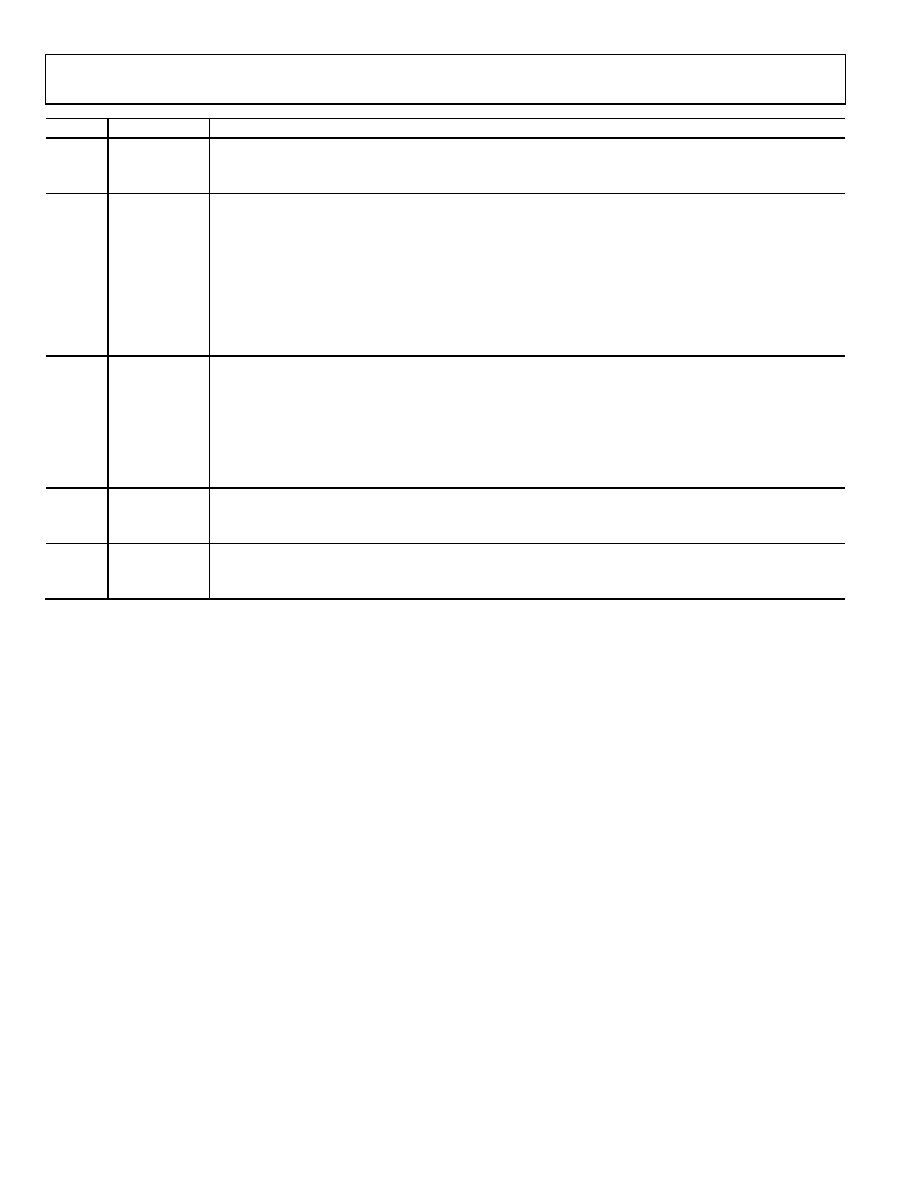

Bit

Name

Description

4

I2CGCCLR

I2C general call status and ID clear bit.

Writing a 1 to this bit clears the general call status and ID bits in the I2CxSSTA register.

This bit is cleared at all other times.

3

I2CHGCEN

I2C hardware general call enable. Hardware general call enable. When this bit and Bit 2 are set, and having

received a general call (Address 0x00) and a data byte, the device checks the contents of the I2CxALT against

the receive register. If the contents match, the device has received a hardware general call. This is used if a

device needs urgent attention from a master device without knowing which master it needs to turn to. This is a

broadcast message to all master devices on the bus. The ADuC7023 watches for these addresses. The device

that requires attention embeds its own address into the message. All masters listen, and the one that can

handle the device contacts its slave and acts appropriately. The LSB of the I2CxALT register should always be

written to 1, as per the I2C January 2000 bus specification.

This bit and I2CGCEN are set to enable hardware general call recognition in slave mode.

This bit is cleared to disable recognition of hardware general call commands.

2

I2CGCEN

I2C general call enable. This bit is set to enable the slave device to acknowledge an I2C general call, Address

0x00 (write). The device then recognizes a data bit. If it receives a 0x06 (reset and write programmable part of

the slave address by hardware) as the data byte, the I2C interface resets as per the I2C January 2000 bus

specification. This command can be used to reset an entire I2C system. If it receives a 0x04 (write programmable part

of the slave address by hardware) as the data byte, the general call interrupt status bit sets on any general call.

The user must take corrective action by reprogramming the device address.

This bit is set to allow the slave acknowledge I2C general call commands.

This bit is cleared to disable recognition of general call commands.

1

ADR10EN

I2C 10-bit address mode.

This bit is set to 1 to enable 10-bit address mode.

This bit is cleared to 0 to enable normal address mode.

0

I2CSEN

I2C slave enable bit.

This bit is set by user to enable I2C slave mode.

This bit is cleared by the user to disable I2C slave mode.

I2C Slave Status Registers, I2CxSSTA

Name:

I2C0SSTA, I2C1SSTA

Address:

0xFFFF082C, 0xFFFF092C

Default value:

0x0000, 0x0000

Access:

Read/write

Function:

These 16-bit MMRs are the I2C status registers in slave mode.

Rev. E

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AIUR-10-182K | INDUCTOR POWER 1800UH 10% T/H |

| EYM15DRSD | CONN EDGECARD 30POS DIP .156 SLD |

| V300C3V3C50B | CONVERTER MOD DC/DC 3.3V 50W |

| AIUR-06-271K | INDUCTOR POWER 270UH 10% T/H |

| EGM15DRSD | CONN EDGECARD 30POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EVAL-ADuC7023QSPZ2 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Precision Analog Microcontroller, 12-Bit Analog I/O, ARM7TDMI MCU with Enhanced IRQ Handler |

| EVALADUC7023QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVAL-ADUC7024QS | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Bulk |

| EVAL-ADUC7024QS-U2 | 制造商:Analog Devices 功能描述:QUICK START DEVL SYST EVAL BOARD I.C. - Bulk |

| EVAL-ADUC7024QS-U3 | 制造商:Analog Devices 功能描述:ARM7 ADUC7024 QUICKSTART DEV KIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。