- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄15530 > EVAL-ADUC7023QSPZ1 (Analog Devices Inc)BOARD EVAL FOR ADUC7023 PDF資料下載

參數(shù)資料

| 型號: | EVAL-ADUC7023QSPZ1 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 19/96頁 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR ADUC7023 |

| 標準包裝: | 1 |

| 系列: | QuickStart™ PLUS 套件 |

| 類型: | MCU |

| 適用于相關產品: | ADuC7023 |

| 所含物品: | 板 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

ADuC7023

Data Sheet

| Page 26 of 96

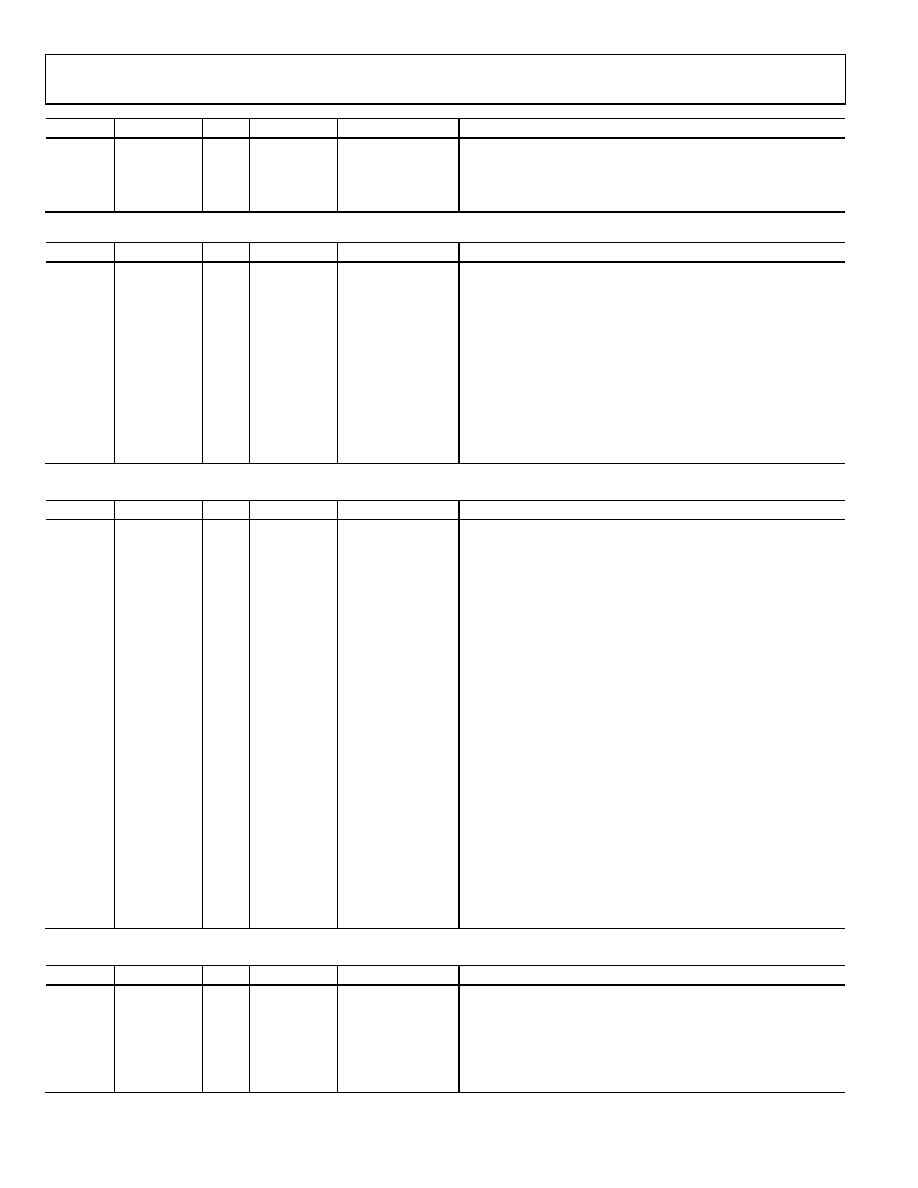

Address

Name

Byte

Access Type

Default Value

Description

0x0530

ADCGN

2

R/W

Factory configured

ADC gain calibration MMR.

0x0534

ADCOF

2

R/W

Factory configured

ADC offset calibration MMR.

0x0544

TSCON

1

R/W

0x00

Temperature sensor chopping enable register.

0x0548

TEMPREF

2

R/W

Factory configured

Temperature sensor reference value.

Table 16. DAC Address Base = 0xFFFF0600

Address

Name

Byte

Access Type

Default Value

Description

0x0600

DAC0CON

1

R/W

0x00

DAC0 control MMR.

0x0604

DAC0DAT

4

R/W

0x00000000

DAC0 data MMR.

0x0608

DAC1CON

1

R/W

0x00

DAC1 control MMR.

0x060C

DAC1DAT

4

R/W

0x00000000

DAC1 data MMR.

0x0610

DAC2CON

1

R/W

0x00

DAC2 control MMR.

0x0614

DAC2DAT

4

R/W

0x00000000

DAC2 data MMR.

0x0618

DAC3CON

1

R/W

0x00

DAC3 control MMR.

0x061C

DAC3DAT

4

R/W

0x00000000

DAC3 data MMR.

0x0654

DACBCFG

1

R/W

0x00

DAC Configuration MMR

0x0650

DACBKEY0

2

W

0x0000

DAC Key0 MMR

0x0658

DACBKEY1

2

W

0x0000

DAC Key1 MMR

Table 17. I2C0 Base Address = 0XFFFF0800

Address

Name

Byte

Access Type

Default Value

Description

0x0800

I2C0MCON

2

R/W

0x0000

I2C0 master control register.

0x0804

I2C0MSTA

2

R

0x0000

I2C0 master status register.

0x0808

I2C0MRX

1

R

0x00

I2C0 master receive register.

0x080C

I2C0MTX

1

W

0x00

I2C0 master transmit register.

0x0810

I2C0MCNT0

2

R/W

0x0000

I2C0 master read count register. Write the number of required

bytes into this register prior to reading from a slave device.

0x0814

I2C0MCNT1

1

R

0x00

I2C0 master current read count register. This register contains the

number of bytes already received during a read from slave sequence.

0x0818

I2C0ADR0

1

R/W

0x00

I2C0 address byte register. Write the required slave address in here

prior to communications.

0x081C

I2C0ADR1

1

R/W

0x00

I2C0 address byte register. Write the required slave address in here

prior to communications. Used in 10-bit mode only.

0x0824

I2C0DIV

2

R/W

0x1F1F

I2C0 clock control register. Used to configure the SCL frequency.

0x0828

I2C0SCON

2

R/W

0x0000

I2C0 slave control register.

0x082C

I2C0SSTA

2

R/W

0x0000

I2C0 slave status register.

0x0830

I2C0SRX

1

R

0x00

I2C0 slave receive register.

0x0834

I2C0STX

1

W

0x00

I2C0 slave transmit register.

0x0838

I2C0ALT

1

R/W

0x00

I2C0 hardware general call recognition register.

0x083C

I2C0ID0

1

R/W

0x00

I2C0 slave ID0 register. Slave bus ID register.

0x0840

I2C0ID1

1

R/W

0x00

I2C0 slave ID1 register. Slave bus ID register.

0x0844

I2C0ID2

1

R/W

0x00

I2C0 slave ID2 register. Slave bus ID register.

0x0848

I2C0ID3

1

R/W

0x00

I2C0 slave ID3 register. Slave bus ID register.

0x084C

I2C0FSTA

2

R/W

0x0000

I2C0 FIFO status register. Used in both master and slave modes.

Table 18. I2C1 Base Address = 0XFFFF0900

Address

Name

Byte

Access Type

Default Value

Description

0x0900

I2C1MCON

2

R/W

0x0000

I2C1 master control register.

0x0904

I2C1MSTA

2

R

0x0000

I2C1 master status register.

0x0908

I2C1MRX

1

R

0x00

I2C1 master receive register.

0x090C

I2C1MTX

1

W

0x00

I2C1 master transmit register.

0x0910

I2C1MCNT0

2

R/W

0x0000

I2C1 master read count register. Write the number of required bytes

into this register prior to reading from a slave device.

Rev. E

相關PDF資料 |

PDF描述 |

|---|---|

| AIUR-10-182K | INDUCTOR POWER 1800UH 10% T/H |

| EYM15DRSD | CONN EDGECARD 30POS DIP .156 SLD |

| V300C3V3C50B | CONVERTER MOD DC/DC 3.3V 50W |

| AIUR-06-271K | INDUCTOR POWER 270UH 10% T/H |

| EGM15DRSD | CONN EDGECARD 30POS DIP .156 SLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EVAL-ADuC7023QSPZ2 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Precision Analog Microcontroller, 12-Bit Analog I/O, ARM7TDMI MCU with Enhanced IRQ Handler |

| EVALADUC7023QSPZU1 | 制造商:Analog Devices 功能描述: |

| EVAL-ADUC7024QS | 制造商:Analog Devices 功能描述:QUICK START DEVELOPMENT SYSTEM - Bulk |

| EVAL-ADUC7024QS-U2 | 制造商:Analog Devices 功能描述:QUICK START DEVL SYST EVAL BOARD I.C. - Bulk |

| EVAL-ADUC7024QS-U3 | 制造商:Analog Devices 功能描述:ARM7 ADUC7024 QUICKSTART DEV KIT |

發(fā)布緊急采購,3分鐘左右您將得到回復。