- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359234 > MT90520AG (ZARLINK SEMICONDUCTOR INC) 8-Port Primary Rate Circuit Emulation AAL1 SAR PDF資料下載

參數(shù)資料

| 型號(hào): | MT90520AG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類(lèi): | 數(shù)字傳輸電路 |

| 英文描述: | 8-Port Primary Rate Circuit Emulation AAL1 SAR |

| 中文描述: | ATM SEGMENTATION AND REASSEMBLY DEVICE, PBGA456 |

| 封裝: | 35 X 35 MM, 1.27 MM PITCH, PLASTIC, MS-034, BGA-456 |

| 文件頁(yè)數(shù): | 74/180頁(yè) |

| 文件大?。?/td> | 1736K |

| 代理商: | MT90520AG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)當(dāng)前第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)

MT90520

Data Sheet

74

Zarlink Semiconductor Inc.

sync

late cell timeout period reached and

CHECK_LATE_ARRIVALS = ‘1’

- UDT RX_SAR inserts a single

dummy cell

late_cell_insertion

invalid sequence number

- accept received cell

invalid

received cell is in sequence with previous cell

- accept received cell

- per-port timeout circuitry is

enabled to permit late-cell

insertions

sync

**

received cell is not in sequence with the

previously-received cell -> received cell has a

sequence number one greater than the

expected sequence number

- assume single-cell loss event

- UDT RX_SAR inserts a single

dummy cell

- after dummy cell insertion, accept

received cell (in-order dummy cell

insertion)

- declare

aal1_seq_error

single_cell_loss_

misinsertion

received cell is not in sequence with the

previously-received cell -> received cell has a

sequence number that is NOT one greater

than the expected sequence number

- cannot assume what happened

(may be a multi-cell loss case)

- accept received cell (thus, if this is

a multi-cell loss case, out-of-order

dummy cell insertion will occur)

- declare

aal1_seq_error

out_of_seq

invalid

invalid sequence number

- discard cell

start

received cell is in sequence with last “good”

cell (i.e., cell misinsertion)

- discard cell

- declare

misinserted_cell_error

- per-port timeout circuitry is

enabled to permit late-cell

insertions

sync

**

received cell has a valid sequence number

that is two greater than the last “good” cell

(i.e., sequence number protection failure)

- accept received cell

- per-port timeout circuitry is

enabled to permit late-cell

insertions

sync

**

received cell has valid sequence number, but

doesn’t meet either of the 2 previous criteria

- discard cell

out_of_sync

out_of_seq

invalid sequence number

- discard cell

start

received cell is in sequence with last received

cell (i.e., multiple cell loss)

- calculate number of lost cells (up

to 7)

- UDT RX_SAR inserts dummy

cell(s)

- after dummy cell insertion(s),

accept received cell

- declare

lost_cell_error

- per-port timeout circuitry is

enabled to permit late-cell

insertions

sync

**

received cell has a valid sequence number

that is two greater than the last in-sequence

cell (i.e., sequence number protection failure)

- accept received cell

- per-port timeout circuitry is

enabled to permit late-cell

insertions

sync

**

received cell has valid sequence number, but

doesn’t meet either of the 2 previous criteria

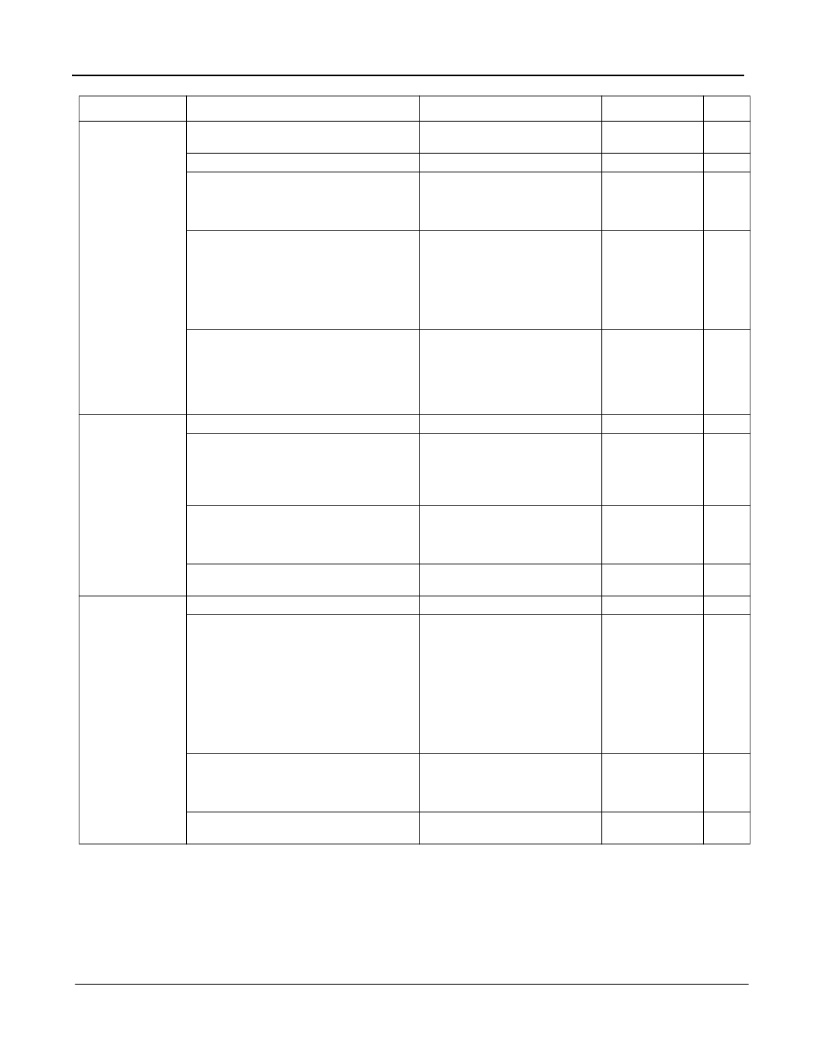

Table 15 - Operation of UDT Fast Sequence Number Processing State Machine

- discard cell

out_of_sync

Current State

Transition Event

Action Taken

Next State

Note

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9072 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT9072AB | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT9072AV | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90820 | Large Digital Switch |

| MT90820AL | Large Digital Switch |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90520AG2 | 制造商:Microsemi Corporation 功能描述:ATM SAR 2.048MBPS 2.5V CBR 456BGA - Trays 制造商:Zarlink Semiconductor Inc 功能描述:ATM SAR 2.048MBPS 2.5V CBR 456BGA - Trays |

| MT90528 | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:28-Port Primary Rate Circuit Emulation AAL1 SAR |

| MT90528AG | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:28-Port Primary Rate Circuit Emulation AAL1 SAR |

| MT90528AG2 | 制造商:ZARLINK 制造商全稱(chēng):Zarlink Semiconductor Inc 功能描述:28-Port Primary Rate Circuit Emulation AAL1 SAR |

| MT90710 | 制造商:MITEL 制造商全稱(chēng):Mitel Networks Corporation 功能描述:High-Speed Isochronous Multiplexer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。