- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384797 > OR4E14 (Lineage Power) Field-Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門陣列) PDF資料下載

參數(shù)資料

| 型號(hào): | OR4E14 |

| 廠商: | Lineage Power |

| 英文描述: | Field-Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門陣列) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門陣列(現(xiàn)場(chǎng)可編程門陣列) |

| 文件頁數(shù): | 62/132頁 |

| 文件大小: | 2667K |

| 代理商: | OR4E14 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁當(dāng)前第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁

62

Lucent Technologies Inc.

Preliminary Data Sheet

August 2000

ORCA Series 4 FPGAs

FPGA States of Operation

(continued)

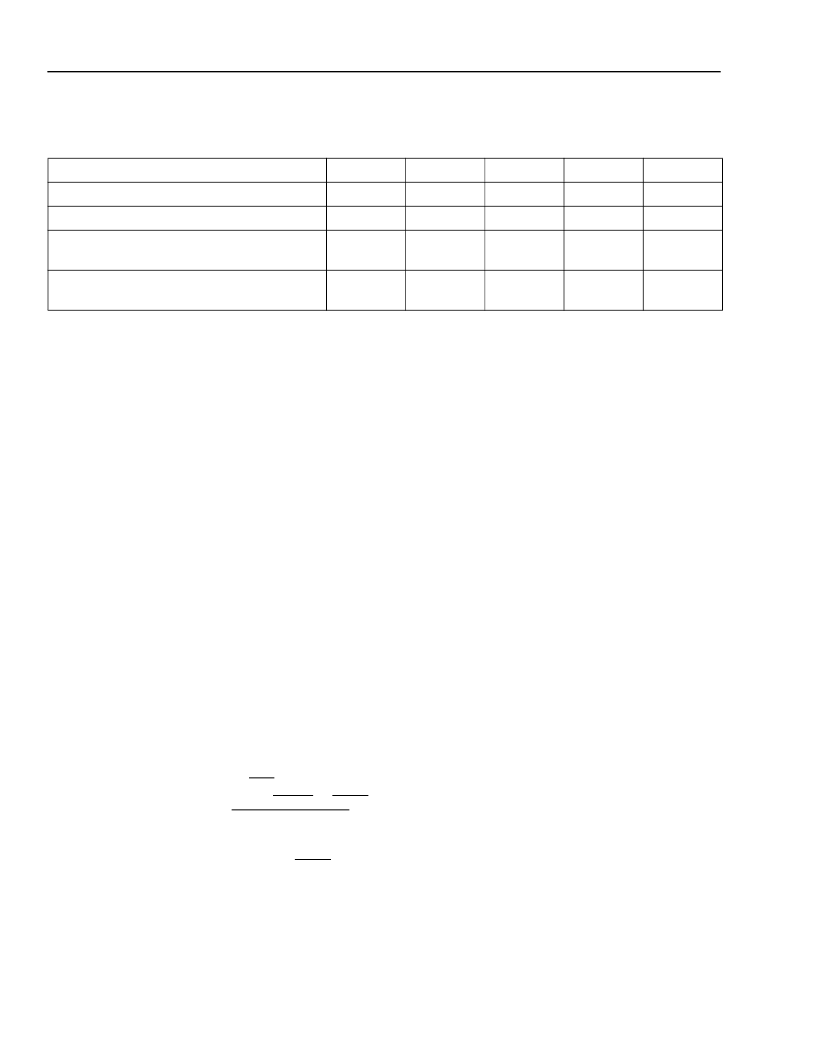

Table 37. Configuration Frame Size

Devices

OR4E2

OR4E4

OR4E6

OR4E10

OR4E14

Number of Frames

1796

2436

3076

3972

4356

Data Bits/Frame

900

1284

1540

1924

2372

Maximum Configuration Data

(Number of bits/frame x Number of frames)

1,610,400

3,127,824

4,737,040

7,642,128

10,332,432

Maximum PROM Size (bits)

(add configuration header and postamble)

1,161,648

3,128,072

4,737,288

7,642,376

10,332,680

Bit Stream Error Checking

There are three different types of bit stream error

checking performed in the ORCA Series 4 FPGAs:

ID frame, frame alignment, and CRC checking.

The ID data frame is sent to a dedicated location in the

FPGA. This ID frame contains a unique code for the

device for which it was generated. This device code is

compared to the internal code of the FPGA. Any differ-

ences are flagged as an ID error. This frame is auto-

matically created by the bit stream generation program

in ORCAFoundry.

Each data and address frame in the FPGA begins with

a frame start pair of bits and ends with eight stop bits

set to 1. If any of the previous stop bits were a 0 when a

frame start pair is encountered, it is flagged as a frame

alignment error.

Error checking is also done on the FPGA for each

frame by means of a checksum byte. If an error is found

on evaluation of the checksum byte, then a checksum/

parity error is flagged. The checksum is the XOR of all

the data bytes, from the start of frame up to and includ-

ing the bytes before the checksum. It applies to the ID,

address, and data frames.

When any of the three possible errors occur, the FPGA

is forced into an idle state, forcing INIT low. The FPGA

will remain in this state until either the

RESET

or

PRGM

pins are asserted. Also the pin CFQ_IRQ/MPI_IRQ is

forced low to signal the error and the specific type of bit

stream error is written to one of the

system bus

regis-

ters by the FPGA configuration logic. The

PGRM

bit of

the

system bus

control register can also be used to

reset out of the error condition and restart configura-

tion.

FPGA Configuration Modes

There are eight methods for configuring the FPGA.

Seven of the configuration modes are selected on the

M0, M1, and M2 inputs. The eighth configuration mode

is accessed through the boundary-scan interface. A

fourth input, M3, is used to select the frequency of the

internal oscillator, which is the source for CCLK in

some configuration modes. The nominal frequencies of

the internal oscillator are 1.25 MHz and 10 MHz. The

1.25 MHz frequency is selected when the M3 input is

unconnected or driven to a high state.

There are three basic FPGA configuration modes:

master, slave, and peripheral. The configuration data

can be transmitted to the FPGA serially or in parallel

bytes. As a master, the FPGA provides the control sig-

nals out to strobe data in. As a slave device, a clock is

generated externally and provided into the CCLK input.

In the three peripheral modes, the FPGA acts as a

microprocessor peripheral. Table 38 lists the functions

of the configuration mode pins.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR4E2 | Field-Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門陣列) |

| OR4E4 | Field-Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門陣列) |

| OR4E6 | Field-Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門陣列) |

| ORT4622 | Field-Programmable System Chip (FPSC) Four Channel x 622 Mbits/s Backplane Transceiver(現(xiàn)場(chǎng)可編程系統(tǒng)芯片(四通道x 622 M位/秒背板收發(fā)器)) |

| ORT8850 | Field-Programmable System Chip(現(xiàn)場(chǎng)可編程系統(tǒng)芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR4E2 | 制造商:AGERE 制造商全稱:AGERE 功能描述:Field-Programmable Gate Arrays |

| OR4E2-1BA256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E2-1BA352 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E2-1BA416 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E2-1BC432 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。