- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383724 > ORT82G5 ORCA ORT82G5 1.0.1-25/2.0-2.5/3.125 Gbits/s Backplane Interface FPSC PDF資料下載

參數(shù)資料

| 型號: | ORT82G5 |

| 英文描述: | ORCA ORT82G5 1.0.1-25/2.0-2.5/3.125 Gbits/s Backplane Interface FPSC |

| 中文描述: | ORCA的ORT82G5 1.0.1-25/2.0-2.5/3.125 Gb /秒背板接口促進(jìn)文化基金 |

| 文件頁數(shù): | 49/92頁 |

| 文件大小: | 1823K |

| 代理商: | ORT82G5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

Agere Systems Inc.

49

Preliminary Data Sheet

July 2001

1.0-1.25/2.0-2.5/3.125 Gbits/s Backplane Interface

ORCA

ORT82G5 FPSC Eight-Channel

Memory Map

(continued)

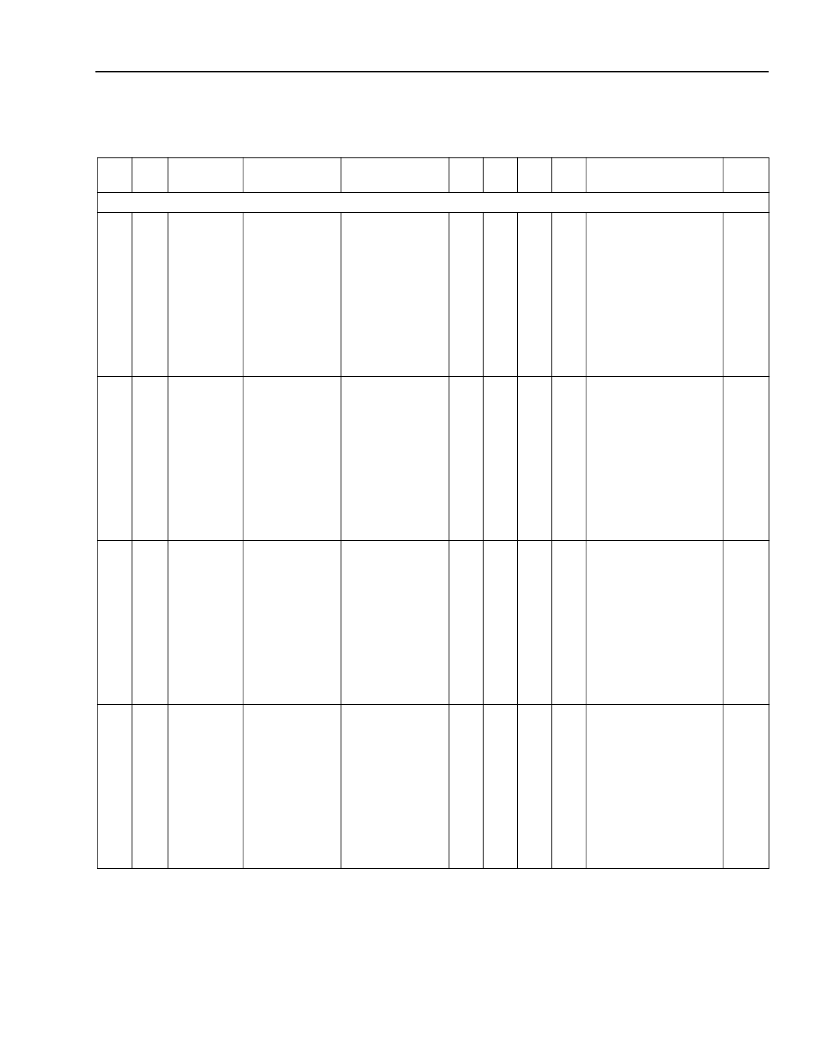

Table 12. Memory Map

(continued)

Addr

(Hex)

Reg

#

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

Default

Value

SERDES B Common Transmit and Receive Channel Configuration Registers

30104

PRBS_BA

Transmit and

Receive PRBS

Enable Bit,

Bank B, Chan-

nel A. When

PRBS = 1, the

PRBS genera-

tor on the trans-

mitter and the

PRBS checker

on the receiver

are enabled.

PRBS = 0 on

device reset.

PRBS_BB

Transmit and

Receive PRBS

Enable Bit,

Bank B, Chan-

nel B. When

PRBS = 1, the

PRBS genera-

tor on the trans-

mitter and the

PRBS checker

on the receiver

are enabled.

PRBS = 0 on

device reset.

PRBS_BC

Transmit and

Receive PRBS

Enable Bit,

Bank B, Chan-

nel C. When

PRBS = 1, the

PRBS genera-

tor on the trans-

mitter and the

PRBS checker

on the receiver

are enabled.

PRBS = 0 on

device reset.

PRBS_BD

Transmit and

Receive PRBS

Enable Bit,

Bank B, Chan-

nel D. When

PRBS = 1, the

PRBS genera-

tor on the trans-

mitter and the

PRBS checker

on the receiver

are enabled.

PRBS = 0 on

device reset.

MASK_BA

Transmit and Receive

Alarm Mask Bit, Bank

B, Channel A. When

MASK = 1, the trans-

mit and receive

alarms of a channel

are prevented from

generating an inter-

rupt. This MASK bit

overrides the individ-

ual alarm mask bits in

the Alarm Mask Reg-

isters. MASK = 1 on

device reset.

MASK_BB

Transmit and Receive

Alarm Mask Bit, Bank

B, Channel B. When

MASK = 1, the trans-

mit and receive

alarms of a channel

are prevented from

generating an inter-

rupt. This MASK bit

overrides the individ-

ual alarm mask bits in

the Alarm Mask Reg-

isters. MASK = 1 on

device reset.

MASK_BC

Transmit and Receive

Alarm Mask Bit, Bank

B, Channel C. When

MASK = 1, the trans-

mit and receive

alarms of a channel

are prevented from

generating an inter-

rupt. This MASK bit

overrides the individ-

ual alarm mask bits in

the Alarm Mask Reg-

isters. MASK = 1 on

device reset.

MASK_BD

Transmit and Receive

Alarm Mask Bit, Bank

B, Channel D. When

MASK = 1, the trans-

mit and receive

alarms of a channel

are prevented from

generating an inter-

rupt. This MASK bit

overrides the individ-

ual alarm mask bits in

the Alarm Mask Reg-

isters. MASK = 1 on

device reset.

SWRST_BA

Transmit and Receive

Software Reset Bit,

Bank B, Channel A.

When SWRST = 1, this

bit provides the same

function as the hard-

ware reset, except all

configuration register

settings are preserved.

This is not a self-clear-

ing bit. Once set, this bit

must be cleared by writ-

ing a 0 to it. SWRST = 0

on device reset.

SWRST_BB

Transmit and Receive

Software Reset Bit,

Bank B, Channel B.

When SWRST = 1, this

bit provides the same

function as the hard-

ware reset, except all

configuration register

settings are preserved.

This is not a self-clear-

ing bit. Once set, this bit

must be cleared by writ-

ing a 0 to it. SWRST = 0

on device reset.

SWRST_BC

Transmit and Receive

Software Reset Bit,

Bank B, Channel C.

When SWRST = 1, this

bit provides the same

function as the hard-

ware reset, except all

configuration register

settings are preserved.

This is not a self-clear-

ing bit. Once set, this bit

must be cleared by writ-

ing a 0 to it. SWRST = 0

on device reset.

SWRST_BD

Transmit and Receive

Software Reset Bit,

Bank B, Channel D.

When SWRST = 1, this

bit provides the same

function as the hard-

ware reset, except all

configuration register

settings are preserved.

This is not a self-clear-

ing bit. Once set, this bit

must be cleared by writ-

ing a 0 to it. SWRST = 0

on device reset.

—

—

—

—

TESTEN_BA

Transmit and Receive Test

Enable Bit, Bank B, Channel A.

When TESTEN = 1, the trans-

mit and receive sections are

placed in test mode. TESTEN

= 0 on device reset. When the

global test enable bit GTES-

TEN = 0, the individual channel

test enable bits are used to

selectively place a channel in

test or normal mode. When

GTESTEN = 1, all channels are

set to test mode regardless of

their TESTEN setting.

TESTEN_BB

Transmit and Receive Test

Enable Bit, Bank B, Channel B.

When TESTEN = 1, the trans-

mit and receive sections are

placed in test mode. TESTEN

= 0 on device reset. When the

global test enable bit GTES-

TEN = 0, the individual channel

test enable bits are used to

selectively place a channel in

test or normal mode. When

GTESTEN = 1, all channels are

set to test mode regardless of

their TESTEN setting.

TESTEN_BC

Transmit and Receive Test

Enable Bit, Bank B, Channel C.

When TESTEN = 1, the trans-

mit and receive sections are

placed in test mode. TESTEN

= 0 on device reset. When the

global test enable bit GTES-

TEN = 0, the individual channel

test enable bits are used to

selectively place a channel in

test or normal mode. When

GTESTEN = 1, all channels are

set to test mode regardless of

their TESTEN setting.

TESTEN_BD

Transmit and Receive Test

Enable Bit, Bank B, Channel D.

When TESTEN = 1, the trans-

mit and receive sections are

placed in test mode. TESTEN

= 0 on device reset. When the

global test enable bit GTES-

TEN = 0, the individual channel

test enable bits are used to

selectively place a channel in

test or normal mode. When

GTESTEN = 1, all channels are

set to test mode regardless of

their TESTEN setting.

02

30114

—

—

—

—

02

30124

—

—

—

—

02

30134

—

—

—

—

02

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ORT8850 | Field-Programmable System Chip (FPSC) Eight-Channel x 850 Mbits/s Backplane Transceiver |

| ORT8850H | Field-Programmable System Chip (FPSC) Eight-Channel x 850 Mbits/s Backplane Transceiver |

| ORT8850L | Field-Programmable System Chip (FPSC) Eight-Channel x 850 Mbits/s Backplane Transceiver |

| OS1001 | Interface IC |

| OS1010 | Optoelectronic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ORT82G5-1BM680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-1BM680I | 功能描述:FPGA - 現(xiàn)場可編程門陣列 10368 LUT 372 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-1F680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 ORCA FPSC 3.7GBITS/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-1F680I | 功能描述:FPGA - 現(xiàn)場可編程門陣列 ORCA FPSC 2.7Gbits/s BP XCVR 643K RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT82G5-1FN680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 ORCA FPSC 1.5V 3.7 G b Bpln Xcvr 643K Gt RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。