- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379877 > celeron processor (Intel Corp.) 32 bit Celeron Processor Mobile Module(32 位帶移動(dòng)模塊處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | celeron processor |

| 廠商: | Intel Corp. |

| 英文描述: | 32 bit Celeron Processor Mobile Module(32 位帶移動(dòng)模塊處理器) |

| 中文描述: | 32位賽揚(yáng)處理器的移動(dòng)模塊(32位帶移動(dòng)模塊處理器) |

| 文件頁數(shù): | 11/64頁 |

| 文件大小: | 799K |

| 代理商: | CELERON PROCESSOR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Celeron

Processor Mobile Module MMC-2

at 650 MHz, 600 MHz, 550 MHz, 500 MHz, and 450 MHz

243357-004

Datasheet

5

I/O D

Input/Open-drain output pin requiring a pullup resistor

I/O

Bi-directional input/output pin

The signal description also includes the type of buffer used for a particular signal:

GTL+

Open-drain GTL+ interface signal

PCI

PCI bus interface signals

AGP

AGP bus interface signals

CMOS

The CMOS signals, depending on functional group, are 1.5V, 2.5V, or 3.3V.

3.1.2

Memory Signal Description

Table 2

provides descriptions of the memory interface signals.

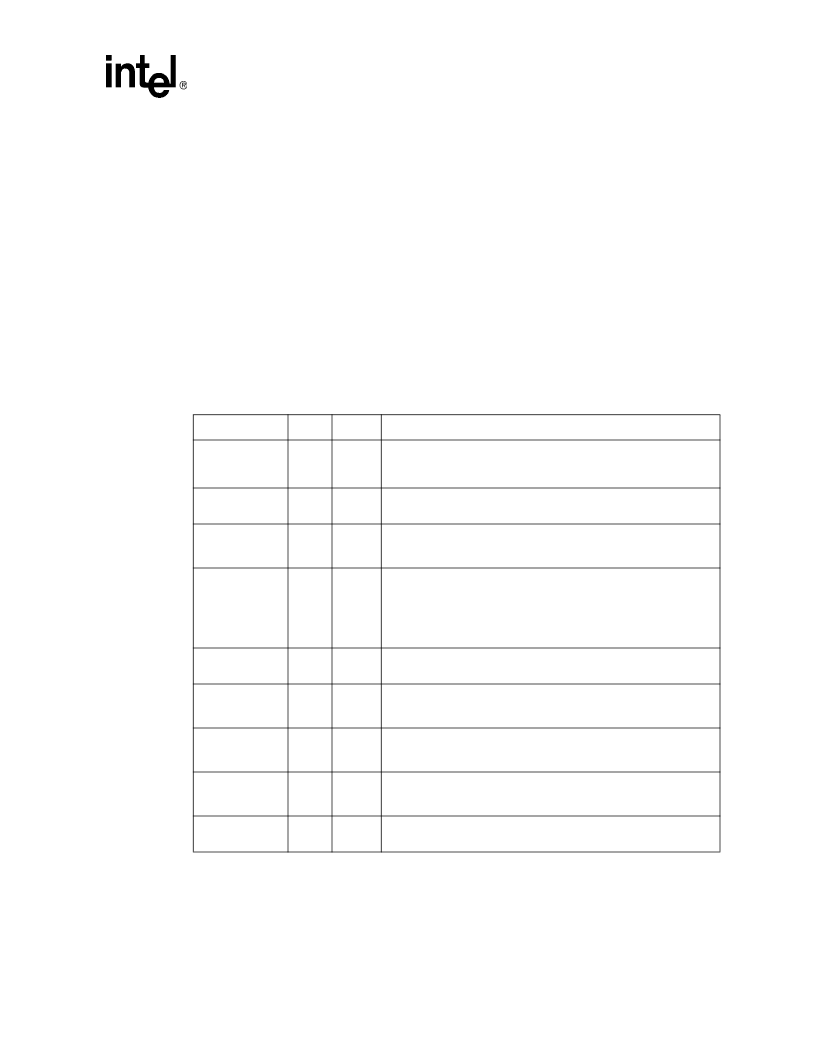

Table 2. Memory Signals

Name

Type

Voltage

Description

MECC[7:0]

I/O

CMOS

V_3

Memory ECC Data:

These signals carry Memory ECC data during

access to DRAM.

ECC is not supported on the mobile module.

CSA[5:O]#

O

CMOS

V_3

Chip Select (SDRAM):

These pins activate the SDRAMs.

SDRAM

accepts any command when its CS# pin is active low.

DQMA[7:0]

O

CMOS

V_3

Input/Output Data Mask (SDRAM):

These pins act as synchronized

output enables during a read cycle and as a byte mask during a write

cycle.

MAB[9:0]#

MAB[10]

MAB[12:11]#

MAB[13]

O

CMOS

V_3

Memory Address (SDRAM):

This is the row and column address for

DRAM.

The 82443BX Host Bridge system controller has two identical

sets of address lines (MAA and MAB#). The mobile module supports

only the MAB set of address lines. For additional addressing features,

please refer to the

Intel

440BX AGPSet: 82443BX Host Bridge/

Controller Datasheet (Order Number: 290633-001).

MWEA#

O

CMOS

V_3

Memory Write Enable (SDRAM):

MWEA# should be used as the

write enable for the memory data bus.

SRASA#

O

CMOS

V_3

SDRAM Row Address Strobe (SDRAM):

When active low, this

signal latches Row Address on the positive edge of the clock. This

signal also allows Row access and pre-charge.

SCASA#

O

CMOS

V_3

SDRAM Column Address Strobe (SDRAM):

When active low, this

signal latches Column Address on the positive edge of the clock.

This

signal also allows Column access.

CKE[5:0]

O

CMOS

V_3

SDRAM Clock Enable (SDRAM):

SDRAM clock enable pin. When

these signals are deasserted, SDRAM enters power-down mode.

Each row is individually controlled by its own clock enable.

MD[63:0]

O

CMOS

V_3

Memory Data:

These signals are connected to the DRAM data bus.

They are not terminated on the mobile module.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CEM11C2 | Dual Enhancement Mode Field Effect Transistor (N and P Channel) |

| CEM2005 | Dual Enhancement Mode Field Effect Transistor(N and Channel) |

| CEM2030A | Dual Enhancement Mode Field Effect Transistor(N and P Channel) |

| CEM2030 | Dual Power MOSFET |

| CEM3310 | Voltage Controlled Envelope Generator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CELF001001J1 | 制造商:Panasonic Industrial Company 功能描述:FILTER |

| CELHK11-1REC5-59-3.00-AV-01-V | 功能描述:CIRCUIT BRKR MAG-HYDR LEVER 3A 制造商:sensata technologies/airpax 系列:CEL 零件狀態(tài):有效 斷路器類型:磁性(液力延遲) 額定電流:3A 額定電壓 - AC:- 額定電壓 - DC:- 極數(shù):2 致動(dòng)器類型:搖臂 照明:- 照明電壓(標(biāo)稱值):- 安裝類型:面板安裝 標(biāo)準(zhǔn)包裝:1 |

| CELHK11-1REC5-59-35.0-AV-01-V | 功能描述:CIRCUIT BRKR MAG-HYDR LEVER 35A 制造商:sensata technologies/airpax 系列:CEL 零件狀態(tài):有效 斷路器類型:磁性(液力延遲) 額定電流:35A 額定電壓 - AC:- 額定電壓 - DC:- 極數(shù):2 致動(dòng)器類型:搖臂 照明:- 照明電壓(標(biāo)稱值):- 安裝類型:面板安裝 標(biāo)準(zhǔn)包裝:1 |

| CELHK11-1REC5-71165-10-V | 功能描述:CIRCUIT BREAKER MAG-HYDR LEVER 制造商:sensata technologies/airpax 系列:* 零件狀態(tài):有效 標(biāo)準(zhǔn)包裝:1 |

| CELHK11-1REC5-71165-11-V | 功能描述:CIRCUIT BREAKER MAG-HYDR LEVER 制造商:sensata technologies/airpax 系列:* 零件狀態(tài):有效 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。