- 您現在的位置:買賣IC網 > PDF目錄383644 > MT90500AL (Mitel Networks Corporation) Multi-Channel ATM AAL1 SAR PDF資料下載

參數資料

| 型號: | MT90500AL |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Multi-Channel ATM AAL1 SAR |

| 中文描述: | 多通道自動柜員機AAL1特區(qū) |

| 文件頁數: | 53/159頁 |

| 文件大小: | 514K |

| 代理商: | MT90500AL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁當前第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁

MT90500

53

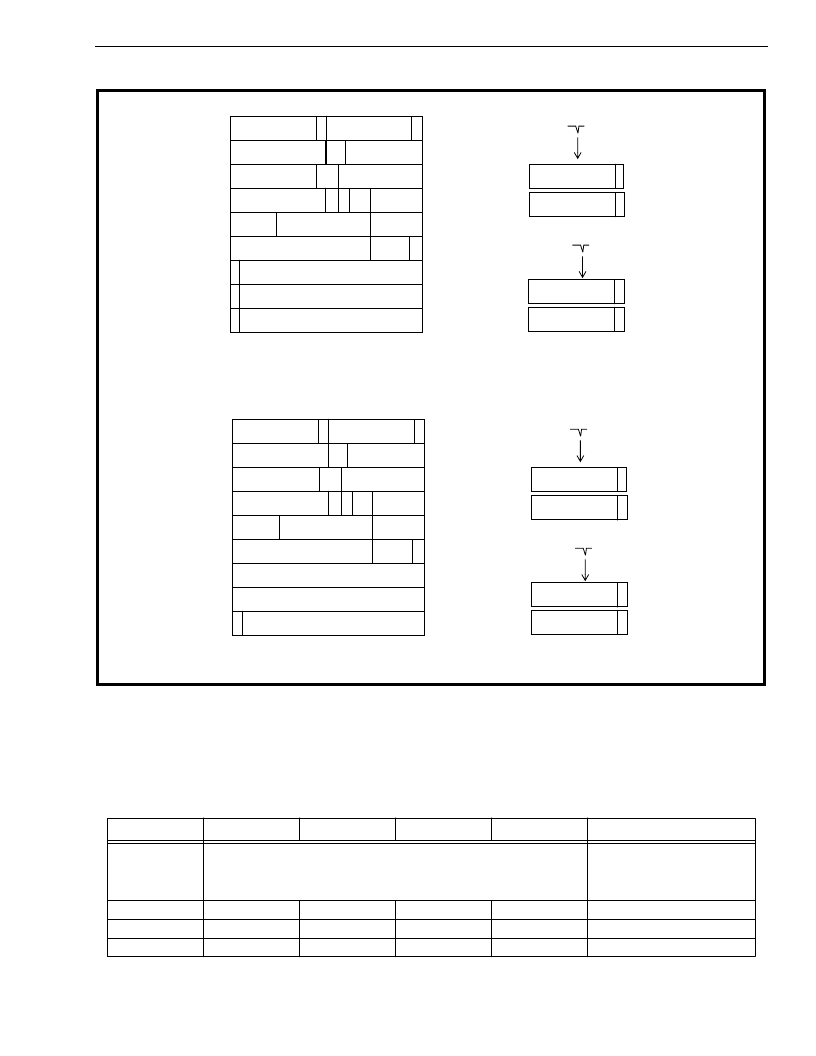

PSEL bits are one-hot bits which represent cells with sequence numbers 0, 2, 4, and 6, respectively - see

Table 10 below for an explanation of bit operation). The MT90500 also supports proprietary pointer

transmissions in which a P-byte is sent every 4 cells (PSEL = A hex) or every other cell (PSEL = F hex). Using

these proprietary methods, up to 122 channels can be sent on a particular VC, but this is only possible if the

receiving chip can handle the extra P-bytes during a cycle.

Each “TX Circular Buffer Address” appended to the end of the structure points to a 64-byte circular buffer in

external memory.

Table 10 - Effect of PSEL Field on P-byte Generation

Sequence # 0

Sequence # 2

Sequence # 4

Sequence #6

Applicable Standards

0000

No pointers are sent.

ANSI and ITU-T

- AAL0, AAL5,

pointerless AAL1 Structured

Data Transfer, and partially-

filled cells

1000

Pointer sent.

-

-

-

ANSI and ITU-T

- AAL1-SDT

1010

Pointer sent

-

Pointer sent

-

ANSI

- AAL1-SDT

1111

Pointer sent

Pointer sent

Pointer sent

Pointer sent

ANSI

- AAL1- SDT

8

15

0

7

First Entry field

1 0 0 0 1 1 0

Last Entry field

1 0 0 1 0 0 0

20180

GFC /

VPI(11:8)

Last Entry

First Entry

Payload Size

Current Entry

PSEL

Offset

HEC

TX Circular Buffer Address

V

0

A

AS

SEQ

Circ. Buf. Pnt.

VPI(7:0)

VCI(15:12)

VCI(11:0)

PTI

R S 00

C1

20182

20184

20186

20188

2018A

2018C

TX Circular Buffer Address

V

2018E

First Entry location = 2018C

TX Circular Buffer Address

V

20190

Last Entry location = 20190

A

A

Figure 18 - a: Sample Three-Channel Transmit Control Structure (AAL1/CBR-AAL0)

0

0

8

15

0

7

First Entry field

1 0 0 1 0 0 0

Last Entry field

1 0 0 1 0 0 0

20180

GFC /

VPI(11:8)

Last Entry

First Entry

Payload Size

Current Entry

PSEL

Offset

HEC

0

A

AS

SEQ

Circ. Buf. Pnt.

VPI(7:0)

VCI(15:12)

VCI(11:0)

PTI

R S 00

C1

20182

20184

20186

20188

2018A

2018C

2018E

First Entry location = 20190

TX Circular Buffer Address

V

20190

Last Entry location = 20190

A

A

0

0

Figure 18 - b: Sample One-Channel Transmit Control Structure (CBR-AAL5)

0000 0000 0000 0000

0000 0000 0000 0000

相關PDF資料 |

PDF描述 |

|---|---|

| MT90502 | Multi-Channel AAL2 SAR(多通道 ATM AAL2分段及重組設備(基于通訊總線的系統(tǒng)與ATM網絡的接口)) |

| MT90732AP | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90732 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90733 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90733AP | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MT90500AL-ENG1 | 制造商:Mitel Networks Corporation 功能描述: |

| MT90502 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-Channel AAL2 SAR |

| MT90502_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-Channel AAL2 SAR |

| MT90502AG | 制造商:Rochester Electronics LLC 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: |

| MT90503 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:2048VC AAL1 SAR |

發(fā)布緊急采購,3分鐘左右您將得到回復。