- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382686 > TSB12C01APZ (Texas Instruments, Inc.) High-Speed Serial-Bus Link-Layer Controller PDF資料下載

參數(shù)資料

| 型號(hào): | TSB12C01APZ |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | High-Speed Serial-Bus Link-Layer Controller |

| 中文描述: | 高速串行總線鏈路層控制器 |

| 文件頁數(shù): | 21/59頁 |

| 文件大小: | 275K |

| 代理商: | TSB12C01APZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

3–5

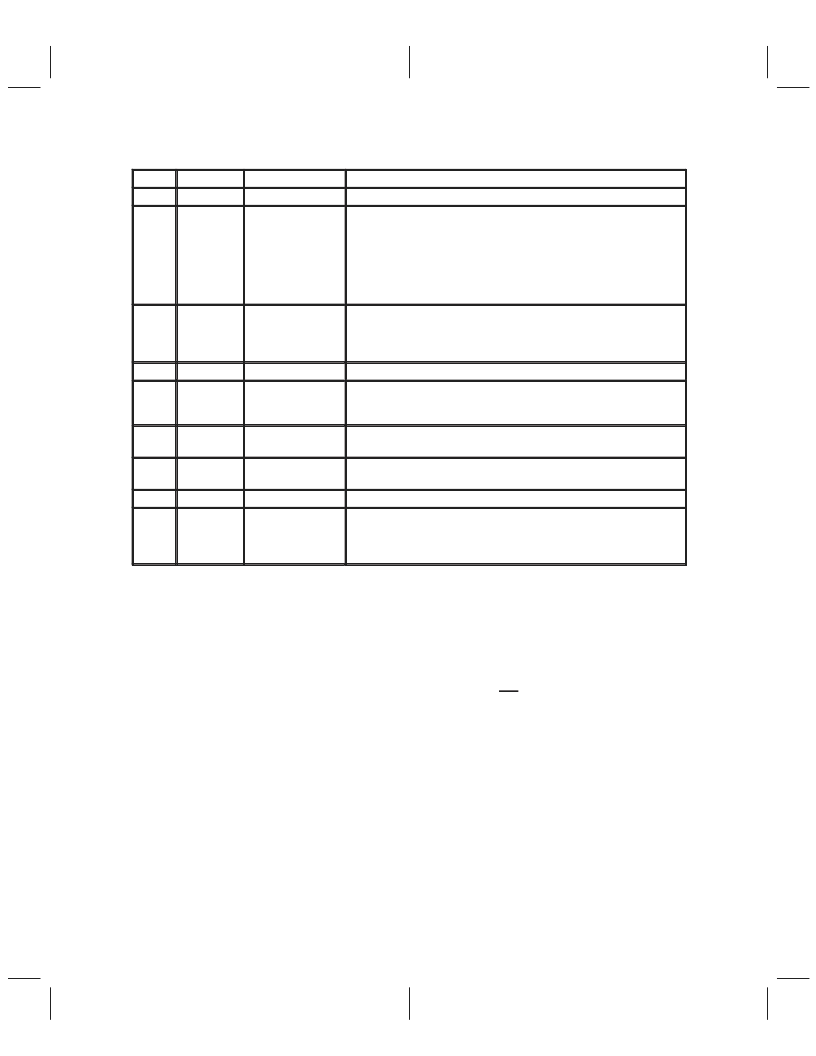

Table 3–3. Control-Register Field Descriptions (Continued)

BITS

ACRONYM

FUNCTION NAME

DESCRIPTION

18–19

Reserved

Reserved

Reserved

20

CyMas

Cycle master

When CyMas is set and the TSB12C01A is attached to the root phy, the

cyclemaster function is enabled. When the cycle_count field of the cycle

timer register increments, the transmitter sends a cycle-start packet.

This bit is not cleared upon bus reset. When another node is selected as

root during a bus reset, the transaction layer in the now nonroot

TSB12C01A node must clear this bit and the transaction layer in the

TSB12C01a node selected as root must set this bit.

21

CySrc

Cycle source

When CySrc is set, the cycle_count field increments and the

cycle_offset field resets for each positive transition of CYCLEIN. When

CySrc is cleared, the cycle_count field increments when the cycle_offset

field rolls over.

22

CyTEn

Cycle-timer enable

When CyTEn is set, the cycle_offset field increments.

23

CyMrkEn

Cycle mark enable

When CyMrkEn is set, cycle marks are inserted into GRF at the end of

each isochronous cycle (TSB12C01A compatible). When CyMrkEn is

cleared, no cycle marks are generated.

24

IRP1En

IR port 1 enable

When IRP1En is set, the receiver accepts isochronous packets when

the channel number matches the value in the IR Port1 field.

25

IRP2En

IR port 2 enable

When IRP2En is set, the receiver accepts isochronous packets when

the channel number matches the value in the IR Port2 field.

26–30

Reserved

Reserved

Reserved

31

RevAEn

Rev A enable

When set, RevAEn enables the output of GRFEMP, CYDNE, and CYST.

When not set, these outputs are in a high-impedance state, which makes

TSB12C01A pin-compatible with the TSB12C01. This bit is 0 on power

up.

3.2.4

The interrupt and interrupt-mask registers work in tandem to inform the host bus interface when the state

of the TSB12C01A changes. The interrupt register is at address 0Ch. The interrupt mask register is at

address 10h. The interrupt mask register is read/write. Its initial value is 0000_0000h. When regRW is

cleared to 0, the interrupt register (except for the Int bit) is write to clear. When regRW (in diagonstics register

at 20h) is set to 1, the interrupt register (including the Int bit) is read/write. Its initial value is 1000_0000h.

Interrupt and Interrupt-Mask Registers

The interrupt bits all work the same. For example, when a phy interrupt occurs, the PhInt bit is set. When

the PhIntMask bit is set, the Int bit is set. When the IntMask is set, the INT signal is asserted. The logic for

the interrupt bits is shown in Figure 3–2. Table 3–4 defines the interrupt and interrupt-mask register field

descriptions. As shown in Figure 3–2, the INT bit is the OR of interrupt bits 1 – 31. When all the interrupt

bits are cleared, INT equals 0. When any of the interrupt bits are set, INT equals 1, even when the INT bit

was just cleared.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB12C01AWN | High-Speed Serial-Bus Link-Layer Controller |

| TSB12LV01APZ | High-Speed Serial-Bus Link-Layer Controller |

| TSB3055 | IC APEX 20KE FPGA 300K 240-PQFP |

| TSB41AB3 | IC APEX 20KE FPGA 400K 672-FBGA |

| TSB41BA3-EP | IC APEX 20KE FPGA 400K 672-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB12C01AWN | 制造商:TI 制造商全稱:Texas Instruments 功能描述:High-Speed Serial-Bus Link-Layer Controller |

| TSB12LV01A | 制造商:Texas Instruments 功能描述: |

| TSB12LV01AIPZ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394 (Firewire) Bus Interface/Controller |

| TSB12LV01APZ | 制造商:TI 制造商全稱:Texas Instruments 功能描述:High-Speed Serial-Bus Link-Layer Controller |

| TSB12LV01B | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394-1995 HIGH SPEED SERIAL BUS LINK LAYER CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。