- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385432 > HYB18L256160B (QIMONDA) DRAMs for Mobile Applications 256-Mbit Mobile-RAM PDF資料下載

參數(shù)資料

| 型號(hào): | HYB18L256160B |

| 廠商: | QIMONDA |

| 英文描述: | DRAMs for Mobile Applications 256-Mbit Mobile-RAM |

| 中文描述: | DRAM的針對(duì)移動(dòng)應(yīng)用256兆移動(dòng)RAM |

| 文件頁數(shù): | 14/58頁 |

| 文件大小: | 1766K |

| 代理商: | HYB18L256160B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

Data Sheet

Rev. 1.73, 2006-09

01302004-CZ2R-J9SE

14

HY[B/E]18L256160B[C/F]L-7.5

256-Mbit Mobile-RAM

2.4

Commands

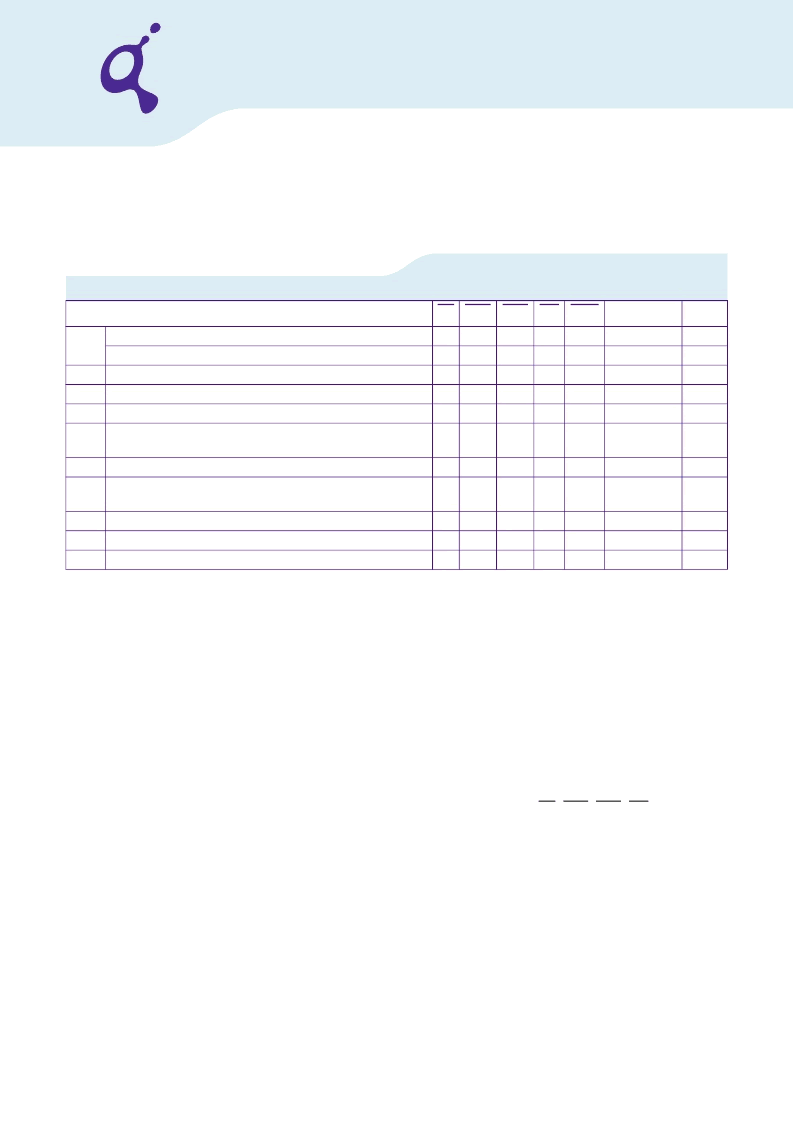

TABLE 8

Command Overview

Address (A0 - A12, BA0, BA1), write data (DQ0 - DQ15) and command inputs (CKE, CS, RAS, CAS, WE, DQM) are all

registered on the positive edge of CLK.

Figure 5

shows the basic timing parameters, which apply to all commands and

operations.

Command

CS

RAS

CAS

WE

DQM

Address

Note

NOP

DESELECT

NO OPERATION

ACTIVE (Select bank and row)

READ (Select bank and column and start read burst)

WRITE (Select bank and column and start write burst)

BURST TERMINATE or

DEEP POWER DOWN

PRECHARGE (Deactivate row in bank or banks)

AUTO REFRESH or

SELF REFRESH (enter self refresh mode)

MODE REGISTER SET

Data Write / Output Enable

Write Mask / Output Disable (High-Z)

H

L

L

L

L

L

X

H

L

H

H

H

X

H

H

L

L

H

X

H

H

H

L

L

X

X

X

L/H

L/H

X

X

X

Bank / Row

Bank / Col

Bank / Col

X

1)

1) DESELECT and NOP are functionally interchangeable.

2) BA0, BA1 provide bank address, and A0 - A12 provide row address.

3) BA0, BA1 provide bank address, A0 - A8 provide column address; A10 HIGH enables the Auto Precharge feature (non persistent), A10

LOW disables the Auto Precharge feature.

4) This command is BURST TERMINATE if CKE is HIGH, DEEP POWER DOWN if CKE is LOW. The BURST TERMINATE command is

defined for READ or WRITE bursts with Auto Precharge disabled only.

5) A10 LOW: BA0, BA1 determine which bank is precharged.

A10 HIGH: all banks are precharged and BA0, BA1 are “Don’t Care”.

6) This command is AUTO REFRESH if CKE is HIGH, SELF REFRESH if CKE is LOW.

7) Internal refresh counter controls row and bank addressing; all inputs and I/Os are “Don’t Care” except for CKE.

8) BA0, BA1 select either the Mode Register (BA0 = 0, BA1 = 0) or the Extended Mode Register (BA0 = 0, BA1 = 1); other combinations of

BA0, BA1 are reserved; A0 - A12 provide the op-code to be written to the selected mode register.

9) DQM LOW: data present on DQs is written to memory during write cycles; DQ output buffers are enabled during read cycles; DQM HIGH:

data present on DQs are masked and thus not written to memory during write cycles;

DQ output buffers are placed in High-Z state (two clocks latency) during read cycles.

1)

ACT

RD

WR

BST

2)

3)

3)

4)

PRE

ARF

L

L

L

L

H

L

L

H

X

X

Code

X

5)

6)7)

MRS

–

–

L

–

–

L

–

–

L

–

–

L

–

–

X

L

H

Op-Code

–

–

8)

9)

9)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYMP112S64LMP8-C4 | DDR2 SDRAM SO-DIMM |

| HYMP112S64LMP8-C5 | DDR2 SDRAM SO-DIMM |

| HYMP112S64LMP8-E3 | BNC FEMALE TO RCA MALE COUPLER |

| HYMP112S64LMP8-E4 | DDR2 SDRAM SO-DIMM |

| HYMP112S64MP8 | SHIELDED, RJ45 TO DB25 ADP, P |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18L256160BC-7.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:BJAWBMSpecialty DRAMs Mobile-RAM |

| HYB18L256160BC-75 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:DRAMs for Mobile Applications |

| HYB18L256160BCL-7.5 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:DRAMs for Mobile Applications 256-Mbit Mobile-RAM |

| HYB18L256160BCX-7.5 | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:DRAMs for Mobile Applications 256-Mbit Mobile-RAM |

| HYB18L256160BF | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:DRAMs for Mobile Applications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。