- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366552 > AM8530 (Advanced Micro Devices, Inc.) Serial Communications Controller PDF資料下載

參數(shù)資料

| 型號: | AM8530 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | Serial Communications Controller |

| 中文描述: | 串行通信控制器 |

| 文件頁數(shù): | 177/194頁 |

| 文件大小: | 797K |

| 代理商: | AM8530 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁當(dāng)前第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁

SCC Application Notes

AMD

7–28

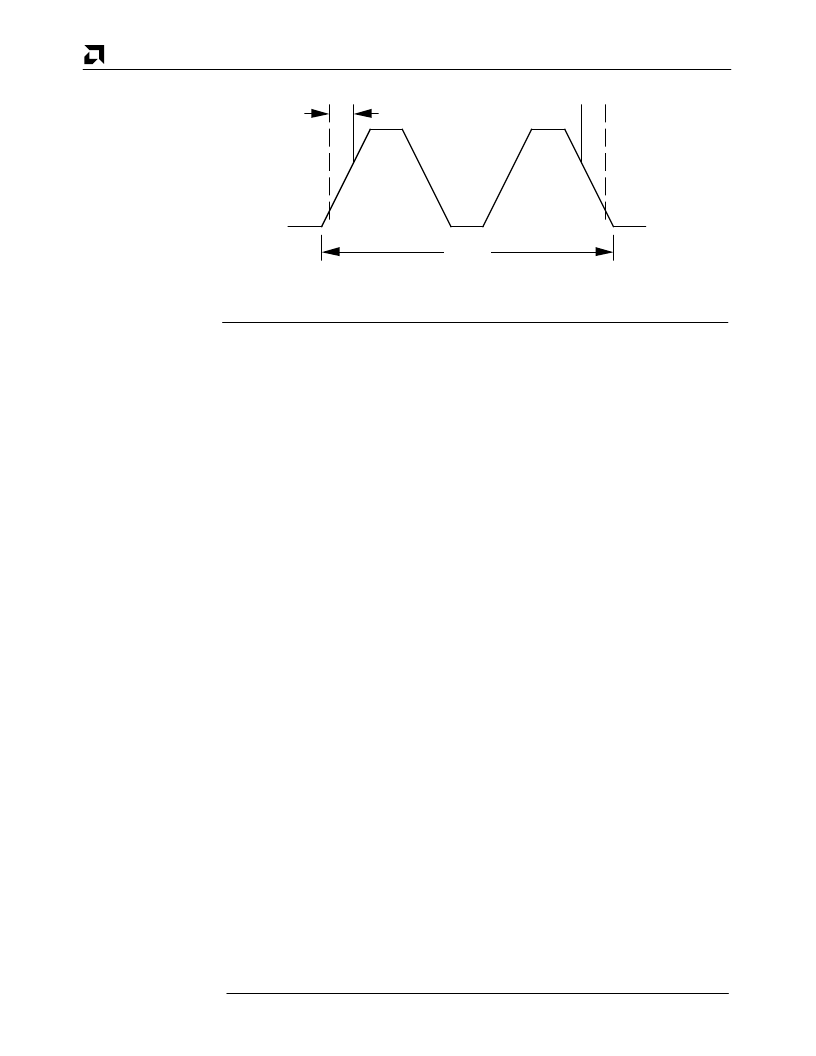

T X C

30% TxC

30% TxC

Figure 7–17. Slew Rate Controlled Outputs

Common-Mode Problem

The common-mode voltage problem can be resolved by using transformer isolation at the

transceiver-cable interface. The Am7960 provides a high impedance interface to the cou-

pling transformer. It also implements a user-transparent Manchester encoding/decoding

scheme that limits the frequency of output data signals to within a narrow range.

Noise Immunity

In the receiver section of the Am7960 a signal qualifier minimizes false starts, thus im-

proving reliability. Line activity is detected when the input signal crosses the threshold.

The receive clock is acquired when there are two transitions of the input signal during a

bit time interval.

Digital S ampling

The internal DPLL runs at 16 times the data rate. Hence, each bit of the received signal is

quantized into 16 samples. The DPLL is free-running when the line is quiet but synchro-

nizes within 1/16 of a bit on the first valid signal edge. It then opens up a series of win-

dows at the 5/16 to 7/16, 12, and 9/16 to 11/16 positions of the expected bit cell.

Zero-crossings within these windows set a Shorten, Center, or Lengthen flag that makes

the loop adjust for sampling of the next bit cell. The internal circuitry samples the incom-

ing data at 1/4 and 3/4 bit intervals. A transition of voltage levels between these two time

slots indicates the arrival of a valid Manchester data bit.

7.6.3

The Am7960 can be used with a Am8530H Serial Communications Controller (SCC) to

build a simple and cost-effective 1 Mb/s data link for office and industrial applications.

The Am8530H is a two channel, software-programmable, device which can adapt to most

system architectures including:

Hardware Considerations

I

Bus architectures (full-duplex and half-duplex)

I

Token Passing Ring (SDLC Loop Mode)

I

STAR Configurations (similar to SLAN)

The power and flexibility of the Am8530H, along with the Am7960’s CSMA-CA access

scheme. Manchester coding of data and output slew rate control enable the system de-

signer to deliver an inexpensive 1 Mb/s LAN.

The straightforward nature of the hardware connections is shown in Figure 7–18. The

Request to Send (

RTS

) output from the SCC is ORed with inverted Advance Carrier De-

tect (

ACD

) output to implement the collision avoidance scheme.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM8530H | Serial Communications Controller |

| AM85C30-10PC | Enhanced Serial Communications Controller |

| Am85C30 | Serial Communications Controller |

| AM85C30 | Enhanced Serial Communications Controller |

| AM85C30-8PC | Enhanced Serial Communications Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM8530ADC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Communications Controller |

| AM8530ADCB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Communications Controller |

| AM8530AJC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Communications Controller |

| AM8530APC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Communications Controller |

| AM8530DC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Communications Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。