- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C970 (Advanced Micro Devices, Inc.) PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C970 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus |

| 中文描述: | PCnetTM - PCI單芯片以太網(wǎng)控制器的PCI總線 |

| 文件頁(yè)數(shù): | 55/168頁(yè) |

| 文件大小: | 943K |

| 代理商: | AM79C970 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)當(dāng)前第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)

AMD

P R E L I M I N A R Y

1-922

Am79C970

Manchester Encoder/Decoder (MENDEC)

The integrated Manchester Encoder/Decoder provides

the PLS (Physical Layer Signaling) functions required

for a fully compliant ISO 8802-3 (IEEE/ANSI 802.3) sta-

tion. The MENDEC provides the encoding function for

data to be transmitted on the network using the high ac-

curacy on-board oscillator, driven by either the crystal

oscillator or an external CMOS level compatible clock.

The MENDEC also provides the decoding function from

data received from the network. The MENDEC contains

a Power On Reset (POR) circuit, which ensures that all

analog portions of the PCnet-PCI controller are forced

into their correct state during power up, and prevents er-

roneous data transmission and/or reception during

thistime.

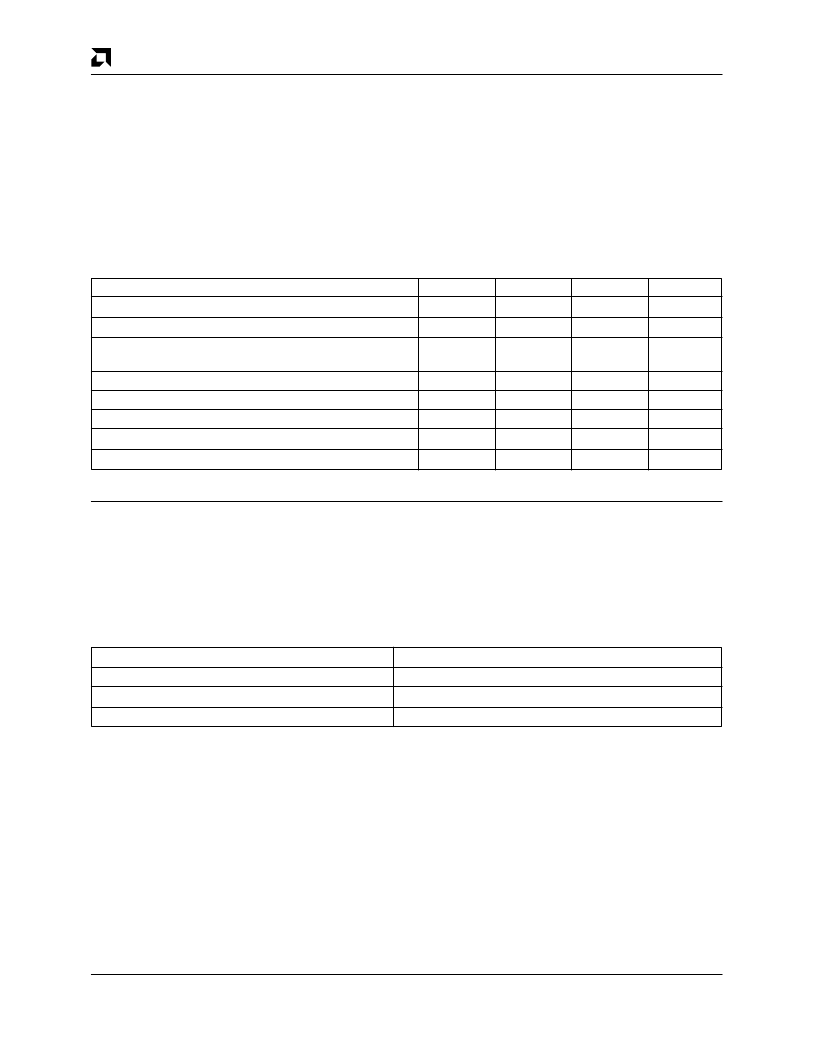

External Crystal Characteristics

When using a crystal to drive the oscillator, the following

crystal specification may be used to ensure less than

±

0.5 ns jitter at DO

±

. See Table 4 below.

Table 4. Crystal Specification

Parameter

Min

Nom

Max

Unit

1. Parallel Resonant Frequency

20

MHz

2. Resonant Frequency Error

–50

+50

PPM

3. Change in Resonant Frequency

With Respect to Temperature (0 – 70

°

C)*

–40

+40

PPM

4. Crystal Load Capacitance

20

50

pF

5. Motional Crystal Capacitance (C1)

0.022

pF

6. Series Resistance

35

7

.

Shunt Capacitance

7

pF

8. Drive Level

TBD

mW

* Requires trimming specification; not trim is 50 PPM total.

External Clock Drive Characteristics

When driving the oscillator from a CMOS level external

clock source, XTAL2 must be left floating (uncon-

nected). Anexternal clock having the following charac-

teristics must be used to ensure less than

±

0.5 ns jitter at

DO

±

. See Table 5.

Table 5. Clock Drive Characteristics

Clock Frequency:

20 MHz

±

0.01%

Rise/Fall Time (t

R

/t

F

):

<= 6 ns from 0.5 V to V

DD

–0.5 V

XTAL1 HIGH/LOW Time (tHIGH/tLOW):

20 ns min

XTAL1 Falling Edge to Falling Edge Jitter:

<

±

0.2 ns at 2.5 V input (V

DD/2

)

MENDEC Transmit Path

The transmit section encodes separate clock and NRZ

data input signals into a standard Manchester encoded

serial bit stream. The transmit outputs (DO

±

) are de-

signed to operate into terminated transmission lines.

When operating into a 78

terminated transmission

line, the transmit signaling meets the required output

levels and skew for Cheapernet, Ethernet and

IEEE-802.3.

Transmitter Timing and Operation

A 20 MHz fundamental mode crystal oscillator provides

the basic timing reference for the MENDEC portion of

the PCnet-PCI controller. The crystal is divided by two,

to create the internal transmit clock reference. Both

clocks are fed into the MENDECs Manchester Encoder

to generate the transitions in the encoded data stream.

The internal transmit clock is used by the MENDEC to

internally synchronize the Internal Transmit Data

(ITXDAT) from the controller and Internal Transmit En-

able (ITXEN). The internal transmit clock is also used as

a stable bit rate clock by the receive section of the MEN-

DEC and controller.

The oscillator requires an external 0.01% timing refer-

ence. The accuracy requirements, if an external crystal

is used are tighter because allowance for the on-board

parasitics must be made to deliver a final accuracy of

0.01%.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C971VCW | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971 | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971KCW | IC LOGIC 16211 24-BIT FET BUS SWITCH -40+85C TSSOP-56 35/TUBE |

| AM79C972BKCW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BKIW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C970A | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC\\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Advanced Micro Devices 功能描述: |

| AM79C970AKC\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。