- 您現(xiàn)在的位置:買賣IC網 > PDF目錄383724 > ORT4622 Field-Programmable System Chip (FPSC) Four-Channel x 622 Mbits/s Backplane Transceiver PDF資料下載

參數(shù)資料

| 型號: | ORT4622 |

| 英文描述: | Field-Programmable System Chip (FPSC) Four-Channel x 622 Mbits/s Backplane Transceiver |

| 中文描述: | 現(xiàn)場可編程系統(tǒng)芯片(促進文化基金)四通道x 622 Mbits /秒背板收發(fā)器 |

| 文件頁數(shù): | 63/90頁 |

| 文件大?。?/td> | 1915K |

| 代理商: | ORT4622 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁當前第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

Lucent Technologies Inc.

Lucent Technologies Inc.

63

Preliminary Data Sheet

March 2000

ORCA ORT4622 FPSC

Four-Channel x 622 Mbits/s Backplane Transceiver

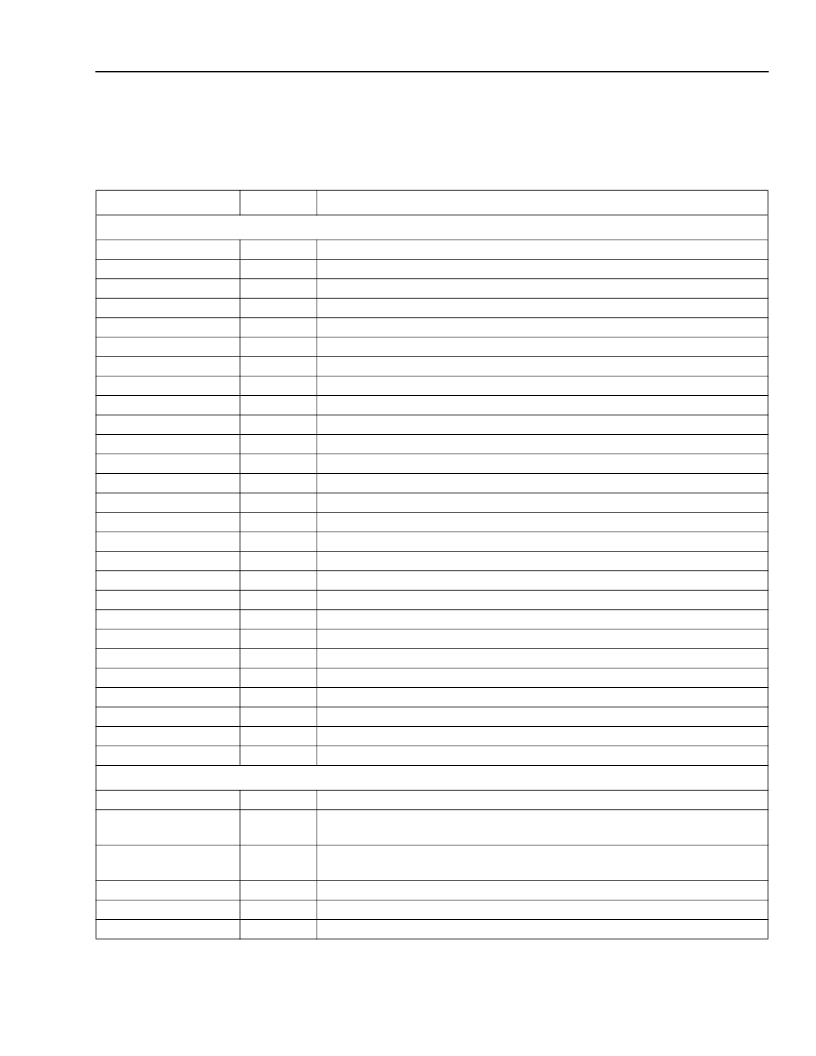

Pin Information

(continued)

This section describes device I/O signals to/from the embedded core excluding the signals at the CIC boundary.

Table 40. FPSC Function Pin Description

Symbol

I/O

Description

HSI LVDS Pins

sts_ina

sts_inan

sts_inb

sts_inbn

sts_inc

sts_incn

sts_ind

sts_indn

sts_outa

sts_outan

sts_outb

sts_outbn

sts_outc

sts_outcn

sts_outd

sts_outdn

ctap_refa

ctap_refb

ctap_refc

ctap_refd

I

I

I

I

I

I

I

I

LVDS input receiver A.

LVDS input receiver A.

LVDS input receiver B.

LVDS input receiver B.

LVDS input receiver C.

LVDS input receiver C.

LVDS input receiver D.

LVDS input receiver D.

LVDS output receiver A.

LVDS output receiver A.

LVDS output receiver B.

LVDS output receiver B.

LVDS output receiver C.

LVDS output receiver C.

LVDS output receiver D.

LVDS output receiver D.

LVDS input center tap (RX A) (use 0.01 μF to GND).

LVDS input center tap (RX B) (use 0.01 μF to GND).

LVDS input center tap (RX C) (use 0.01 μF to GND).

LVDS input center tap (RX D) (use 0.01 μF to GND).

LVDS reference voltage: 1.0 V ± 3%.

LVDS reference voltage: 1.4 V ± 3%.

Resistor input (use 100

± 1% to RESLO input).

Resistor input.

Reference resistor for PLL (10 k

to ground).

PLL analog V

DD

(3.3 V

±

5%).

PLL analog V

SS

(GND).

O

O

O

O

O

O

O

O

—

—

—

—

I

I

—

—

—

—

—

ref10

ref14

reshi

reslo

rext

pll_V

DD

A

pll_V

SS

A

HSI Test Signals

tstmode

bypass

I

I

Enables CDR test mode. Internal pull-down.

Enables bypassing of the 622 MHz clock synthesis with TSTCLK. Internal

pull-down.

Test clock for emulation of 622 MHz clock during PLL bypass. Internal pull-

down.

Test mode reset. Internal pull-down.

Resets receiver clock division counter. Internal pull-up.

Resets transmitter clock division counter. Internal pull-up.

tstclk

I

mreset

resetrn

resettn

I

I

I

相關PDF資料 |

PDF描述 |

|---|---|

| ort551 | Reed Switch(舌簧開關) |

| ord2210v | Reed Switch(舌簧開關) |

| ord2210 | Reed Switch(舌簧開關) |

| ord211 | Reed Switch(舌簧開關) |

| ord2211 | Reed Switch(舌簧開關) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ORT4622BC432-DB | 功能描述:FPGA - 現(xiàn)場可編程門陣列 10368 LUT 204 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT551 | 制造商:Hasco Components International Corp 功能描述: |

| ORT551(1315) | 制造商:OKI Semiconductor 功能描述: |

| ORT551/10-15 AT | 功能描述:磁性/簧片開關 1 Form C 14mm AT 1015 OKI RoHS:否 制造商:MEDER electronic (Standex) 開關類型:Reed 觸點形式:1 Form A (SPST-NO) 觸點額定值:10 VA 操作范圍:10 At to 50 At 工作間隙: 磁鐵類型: 顏色: 端接類型:Axial 封裝:Bulk |

| ORT551-1/10-15 AT | 功能描述:磁性/簧片開關 1 Form C 14mm AT1015 Formed Ld OKI RoHS:否 制造商:MEDER electronic (Standex) 開關類型:Reed 觸點形式:1 Form A (SPST-NO) 觸點額定值:10 VA 操作范圍:10 At to 50 At 工作間隙: 磁鐵類型: 顏色: 端接類型:Axial 封裝:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。