- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383724 > ORT4622 Field-Programmable System Chip (FPSC) Four-Channel x 622 Mbits/s Backplane Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | ORT4622 |

| 英文描述: | Field-Programmable System Chip (FPSC) Four-Channel x 622 Mbits/s Backplane Transceiver |

| 中文描述: | 現(xiàn)場(chǎng)可編程系統(tǒng)芯片(促進(jìn)文化基金)四通道x 622 Mbits /秒背板收發(fā)器 |

| 文件頁(yè)數(shù): | 41/90頁(yè) |

| 文件大?。?/td> | 1915K |

| 代理商: | ORT4622 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)當(dāng)前第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)

Lucent Technologies Inc.

41

Preliminary Data Sheet

March 2000

ORCA ORT4622 FPSC

Four-Channel x 622 Mbits/s Backplane Transceiver

Electrical Characteristics

(continued)

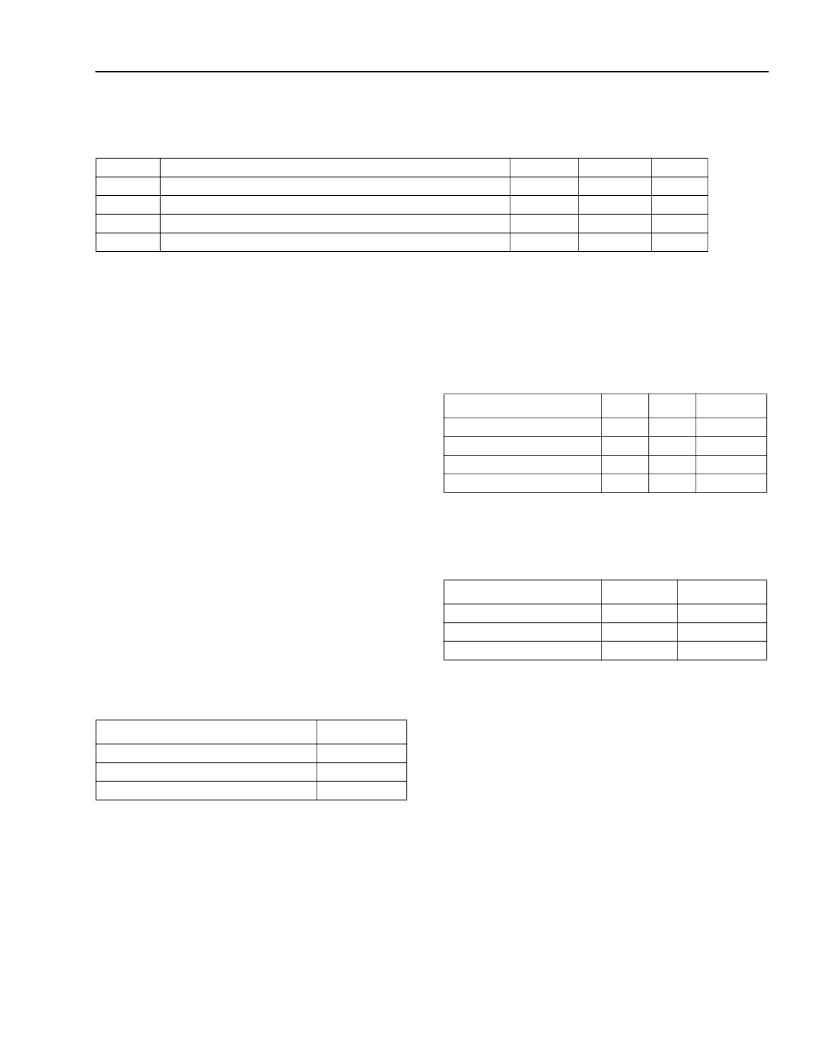

Table 17. Electrical Characteristics for Embedded Core I/O Other than LVDS I/O

Note: All outputs are driving 35 pF, except CPU data bus pins which drive 100 pF. It is assumed that the TTL buffers from the

standard-cell library can handle the 100 pF load.

Symbol

V

IH

V

IL

V

OH

V

OH

Parameter

Min

2.0

—

2.4

—

Max

5.5

0.8

—

0.4

Unit

V

V

V

V

Input High Voltage (TTL input)

Input Low Voltages (TTL input)

Output High Voltage (TTL output)

Output Low Voltage (TTL output)

HSI Circuit Specifications

Input Data

The 622 Mbits/s scrambled input data stream must

conform to SONET STS-12 and SDH STM-4 data for-

mat using either a PN7 or PN9 sequence. The PN7

characteristic is 1 + x

6

+ x

7

and the PN9 characteristic

is 1 + x

4

+ x

9

. The ORT4622 supplies a default scram-

bler using the PN7 sequence. The longest allowable

stream of nontransitional 622 Mbits/s input data is 60

bits. This sequence should not occur more often than

once per minute. An input signal phase change of no

more than 100 ps is allowed over 200 ns time interval,

which translates to a frequency change of 500 ppm.

The signal eye opening must be greater than 0.4 UIp-p

(unit interval peak-to-peak), and the unit interval for

622 Mbits/s is 1.6075 ns.

Jitter Tolerance

The input jitter tolerance of the ORT4622 is shown in

Table 18.

Table 18. Jitter Tolerance

Generated Output Jitter

The generated output jitter is a maximum of 0.2 UIp-p

from 250 kHz to 5 MHz.

PLL

PLL requires an external 10 k

pull-down resistor.

Table 19. PLL

Input Reference Clock

Table 20. Input Reference Clock

Frequency

250 kHz

25 kHz

2 kHz

UIp-p

0.6

6.0

60

Parameter

Min

—

—

10

—

Max

6

2

—

1

Unit

MHz

dB

μs

ms

Loop Bandwidth

Jitter Peaking

Powerup Reset Duration

Lock Acquisition

Parameter

Min

—

—

—

Max

Frequency Deviation

Frequency Change

Phase Change in 200 ns

±

20 ppm

500 ppm

100 ps

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ort551 | Reed Switch(舌簧開關(guān)) |

| ord2210v | Reed Switch(舌簧開關(guān)) |

| ord2210 | Reed Switch(舌簧開關(guān)) |

| ord211 | Reed Switch(舌簧開關(guān)) |

| ord2211 | Reed Switch(舌簧開關(guān)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ORT4622BC432-DB | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門陣列 10368 LUT 204 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| ORT551 | 制造商:Hasco Components International Corp 功能描述: |

| ORT551(1315) | 制造商:OKI Semiconductor 功能描述: |

| ORT551/10-15 AT | 功能描述:磁性/簧片開關(guān) 1 Form C 14mm AT 1015 OKI RoHS:否 制造商:MEDER electronic (Standex) 開關(guān)類型:Reed 觸點(diǎn)形式:1 Form A (SPST-NO) 觸點(diǎn)額定值:10 VA 操作范圍:10 At to 50 At 工作間隙: 磁鐵類型: 顏色: 端接類型:Axial 封裝:Bulk |

| ORT551-1/10-15 AT | 功能描述:磁性/簧片開關(guān) 1 Form C 14mm AT1015 Formed Ld OKI RoHS:否 制造商:MEDER electronic (Standex) 開關(guān)類型:Reed 觸點(diǎn)形式:1 Form A (SPST-NO) 觸點(diǎn)額定值:10 VA 操作范圍:10 At to 50 At 工作間隙: 磁鐵類型: 顏色: 端接類型:Axial 封裝:Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。