- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385396 > HSP50214VC (INTERSIL CORP) Programmable Downconverter PDF資料下載

參數(shù)資料

| 型號: | HSP50214VC |

| 廠商: | INTERSIL CORP |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Programmable Downconverter |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP120 |

| 封裝: | MQFP-120 |

| 文件頁數(shù): | 45/54頁 |

| 文件大小: | 395K |

| 代理商: | HSP50214VC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

45

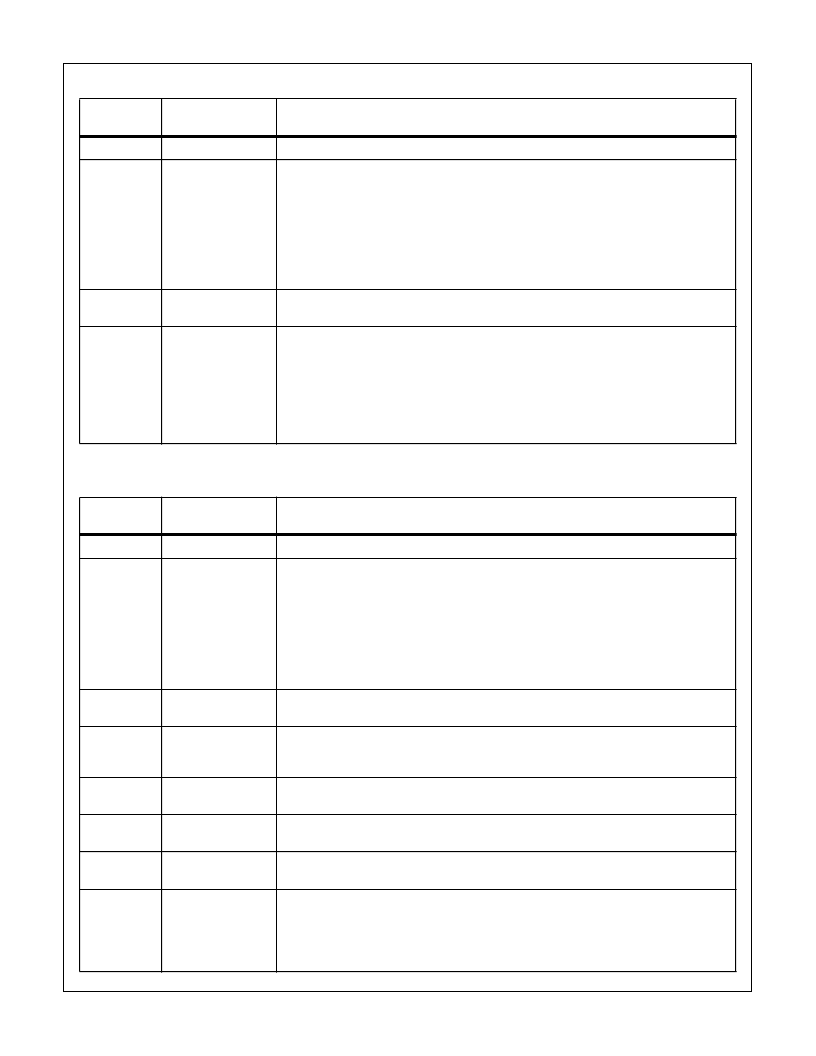

CONTROL WORD 16: RE-SAMPLING FILTER CONTROL (SYNCHRONIZED TO PROCCLK)

BIT

POSITION

FUNCTION

DESCRIPTION

31-12

Reserved

Reserved.

11-4

Resampler Output

Pulse Delay

NOTE: These bits program the delay between output samples when interpolating. The extra out-

puts can be delayed from 2 to 255 clocks from the first output. A delay of 2 equals 255

clocks of delay. A delay of 0 or 1 is an invalid mode. When interpolating by 2, one extra

output is generated; when interpolating by 4, 3 extra outputs are generated. Program by

the equation (PROCCLK/f

OUT

) - 1. Bit 11 is the MSB.

NOTE: If less than 5 is programmed, there will not be sufficient time to fully update the out-

put buffer. If less than 16 is programmed, the serial output may be preempted. This

means that it won’t finish and if the sync is programmed to follow the data, there

may never be a sync.

3

Resampler Bypass

0- Re-Sampling Filter Enabled. A valid combination of bits 2-0 must also be selected.

1- Re-Sampling Filter is Bypassed.

2-0

Filter Mode Select;

2- HB2 Enabled

1- HB1 Enabled

0- Resampler

Enabled

000- Not Valid.

001- Resampler Enabled.

010- Halfband 1 Enabled.

011- Resampler and Halfband Filter 1 Enabled.

100- Not Valid.

101- Not Valid.

110- Both Halfband Filters Enabled.

111- Resampler and Both Halfband Filters Enabled.

CONTROL WORD 17: DISCRIMINATOR FILTER CONTROL, DISCRIMINATOR DELAY (SYNCHRONIZED TO PROCCLK)

BIT

POSITION

FUNCTION

DESCRIPTION

31-17

Reserved

Reserved.

16-15

Phase Multiplier

These bits program allow the phase output of the cartesian to polar converter to be multiplied by

1, 2, 4, or 8 (modulo 2

π

) to remove phase modulation before the frequency is measured.

00- No Shift on Phase Input to frequency discriminator.

01- Shift Phase Input to frequency discriminator up 1 (one bit), discarding the MSB and zero filling

the LSB.

10- Shift Phase Input to frequency discriminator up 2 (two) bits, discarding the MSB and zero fill-

ing the LSB.

11- Shift Phase Input to frequency discriminator up 3 (three) bits, discarding the MSB and zero

filling the LSB.

14

Discriminator Enable

0- Disable Discriminator.

1- Enable Discriminator.

13-11

Discriminator FIR

Decimation

The decimation can be programmed from 1 to 8, where 000 = decimate by 8; 001 = decimate by

1; 010 = decimate by 2; 011 = decimate by 3; 100 = decimate by 4; 101 = decimate by 5; 110 =

decimate by 6; and 111 - decimate by 7.

10

FIR Symmetry Type

0- Odd Symmetry.

1- Even Symmetry.

9

FIR Symmetry

0- Symmetric.

1- Asymmetric.

8-3

Number of FIR Taps

Number of FIR taps from 1 to 63, where 00000 is not valid (00001 = 1 tap, 00010 = 2 taps, etc.

up to 11111 = 63 taps). Bit 8 is the MSB.

2-0

Discriminator Delay

Sets the number of delays from 1 to 8 in the discriminator. Set delay ddd to delay minus 1,

where 000 represents 1 delay; 001 represents 2 delays, 010 represents 3 delays, 011 repre-

sents 4 delays, 100 represents 5 delays, 101 represents 6 delays, 110 represents 7 delays, and

111 represents 8 delays. If ddd the decimal representation bits 2-0, then the discriminator a

transfer function H(Z) = 1-Z

-(ddd + 1)

.

HSP50214

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50214VI | Programmable Downconverter |

| HSP50214 | Programmable Downconverter |

| HSP50215VC | Digital UpConverter |

| HSP50215VI | Digital UpConverter |

| HSP50215EVAL | DSP Modulator Evaluation Board |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50214VI | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP50215 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:DSP Modulator Evaluation Board |

| HSP50215EVAL | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:DSP Modulator Evaluation Board |

| HSP50215VC | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital UpConverter |

| HSP50215VI | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Digital UpConverter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。