- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384806 > OXCB950 (Electronic Theatre Controls, Inc.) Integrated High Performance UART Cardbus / PCI interface PDF資料下載

參數(shù)資料

| 型號(hào): | OXCB950 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Integrated High Performance UART Cardbus / PCI interface |

| 中文描述: | 綜合高性能的UART Cardbus / PCI接口 |

| 文件頁(yè)數(shù): | 4/68頁(yè) |

| 文件大小: | 409K |

| 代理商: | OXCB950 |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

1 P

ERFORMANCE

C

OMPARISON

Data Sheet Revision 1.1

Page 4

OXCB950

OXFORD SEMICONDUCTOR LTD.

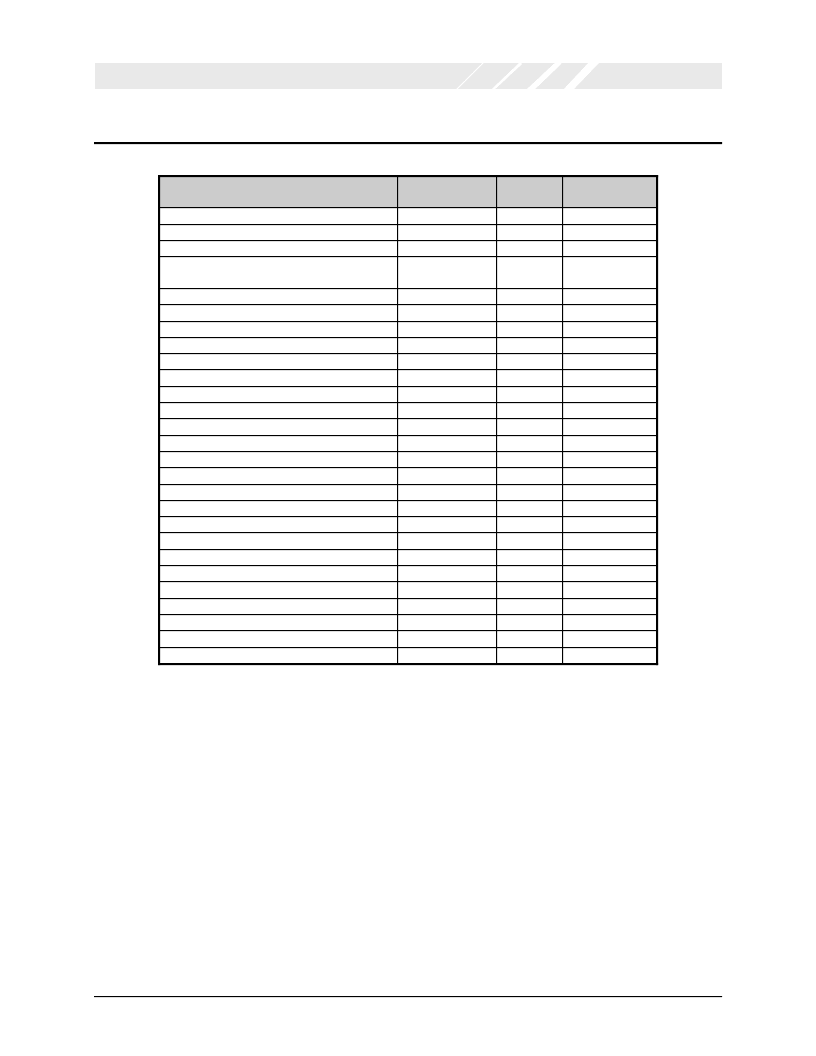

Feature

OXCB950

16C550 +

PLX9050

no

no

2

no

16C650 +

PLX9050

No

No

2

No

Support for PCI Power Management

Zero wait-state read/write operation

No. of external interrupt source pins

DWORD access to UART Interrupt Source

Registers & FIFO Levels

Good-Data status

Full Plug and Play with external EEPROM

External 1x baud rate clock

Max baud rate in normal mode

Max baud rate in 1x clock mode

FIFO depth

Sleep mode

Auto Xon/Xoff flow

Auto CTS#/RTS#flow

Auto DSR#/DTR# flow

No. of Rx interrupt thresholds

No. of Tx interrupt thresholds

No. of flow control thresholds

Transmtter empty interrupt

Readable status of flow control

Readable FIFO levels

Clock prescaler options

Rx/Tx disable

Software reset

Device ID

9-bit data frames

RS485 buffer enable

Infra-red (IrDA)

yes

yes

2

yes

yes

yes

yes

no

yes

no

No

Yes

No

15 Mbps

60 Mbps

128

yes

yes

yes

yes

128

128

128

yes

yes

yes

248

yes

yes

yes

yes

yes

yes

115 Kbps

n/a

16

no

no

no

no

4

1

n/a

no

no

no

n/a

no

no

no

no

no

no

1.5 Mbps

n/a

64

Yes

Yes

Yes

No

4

4

4

No

No

No

2

No

No

No

No

No

Yes

Table 1: OXCB950 performance compared with PLX + generic UART combinations in PCI mode

1.1

Improvements of the OXCB950 over discrete solutions:

Improved access timing:

Access to the internal UART requires zero or one PCI wait states. A cardbus/PCI read transaction fromthe internal UART can

complete within five PCI clock cycles and a write transaction to the internal UART can complete within four PCI clock cycles.

Reduces interrupt latency:

The OXCB950 offers shadowed FIFO levels and Interrupt status registers of the internal UART, as well as general device

interrupt status, to reduce the device driver interrupt latency.

Power management:

The OXCB950 complies with the Cardbus Power Management Specification, given by the PC CARD standard release 7.0/7.1,

the PCI Power Management Specification 1.0 and the PC98/99 Power Management specifications, by offering the extended

capabilities for Power Management and supporting the power states D0, D2 and D3. This achieves significant power savings by

allowing device drivers to power down the cardbus/PCI function and disable the UART channel.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OXFW900 | IEEE1394 to ATA/ATAPI Native Bridge |

| OXFW900-TQ-A | IEEE1394 to ATA/ATAPI Native Bridge |

| OXFW911 | IEEE1394 to ATA/ATAPI Native Bridge |

| OXFW911-TQ-A | IEEE1394 to ATA/ATAPI Native Bridge |

| OZ6812 | ACPI CardBus Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OXCB950-TQAG | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 32 bit PC Card bridge to serial prt RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| OXCB950-TQC60-A | 制造商:OXFORD 制造商全稱(chēng):OXFORD 功能描述:Integrated High Performance UART Cardbus / 3.3v PCI interface |

| OXCF950 | 制造商:OXFORD 制造商全稱(chēng):OXFORD 功能描述:low cost asynchronous 16-bit PC card or Compact Flash UART device |

| OXCF950_06 | 制造商:OXFORD 制造商全稱(chēng):OXFORD 功能描述:low cost asynchronous 16-bit PC card or Compact Flash UART device |

| OXCF950B | 制造商:PLX 制造商全稱(chēng):PLX 功能描述:16-bit PC card/CF+ bridge to serial port |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。