- 您現(xiàn)在的位置:買賣IC網 > PDF目錄367625 > MFRC53101T (NXP Semiconductors N.V.) ISO-IEC 14443 reader IC PDF資料下載

參數(shù)資料

| 型號: | MFRC53101T |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 通信及網絡 |

| 英文描述: | ISO-IEC 14443 reader IC |

| 封裝: | MFRC53101T/0FE<SOT287-1 (SO32)|<<http://www.nxp.com/packages/SOT287-1.html<1<week 51, 2004,;MFRC53101T/0FE<SOT287-1 (SO32)|<<http://www.nxp.com/packages/SOT287-1.html< |

| 文件頁數(shù): | 104/116頁 |

| 文件大?。?/td> | 862K |

| 代理商: | MFRC53101T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁當前第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

MFRC531_34

NXP B.V. 2010. All rights reserved.

Product data sheet

PUBLIC

Rev. 3.4 — 26 January 2010

056634

104 of 116

NXP Semiconductors

MFRC531

ISO/IEC 14443 reader IC

15.2.3

Digital test signals

Digital test signals can be routed to pin MFOUT by setting bit SignalToMFOUT = logic 1. A

digital test signal is selected using the TestDigiSelect register TestDigiSignalSel[6:0] bits.

The signals selected by the TestDigiSignalSel[6:0] bits are shown in

Table 166

.

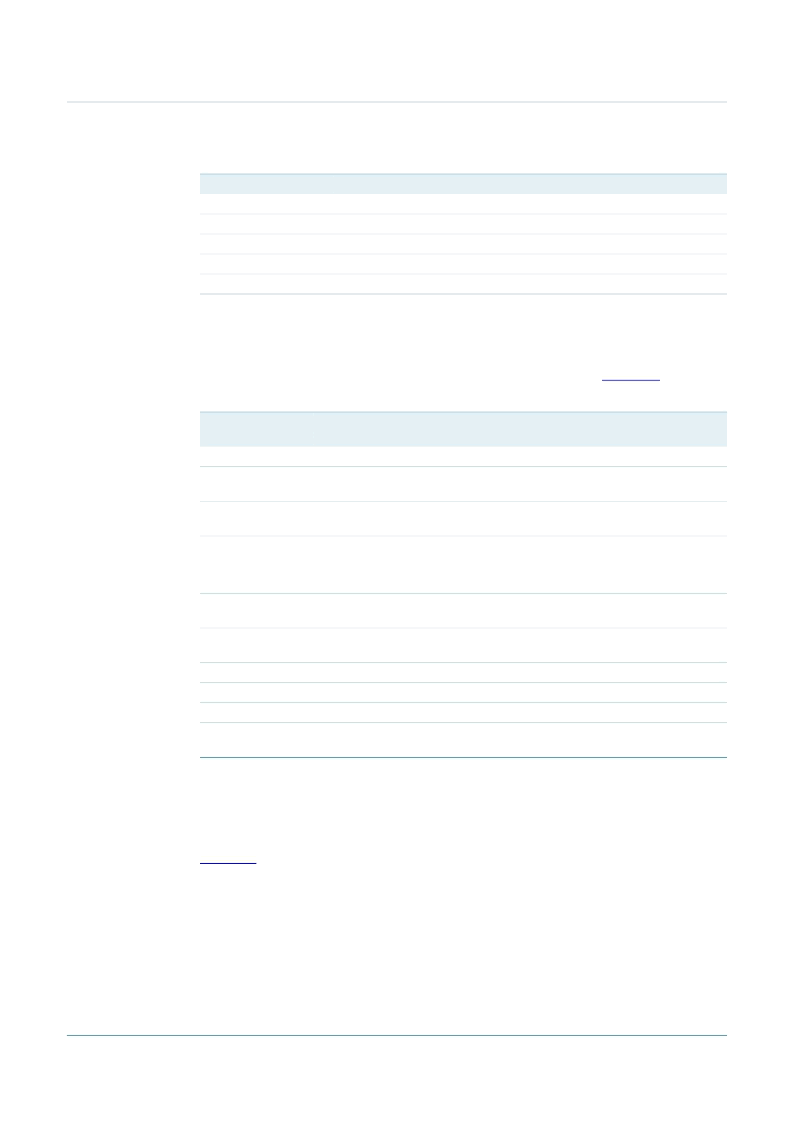

Table 166. Digital test signal selection

TestDigiSignalSel

[6:0]

F4h

E4h

If test signals are not used, the TestDigiSelect register address value must be 00h.

Remark:

All other values for TestDigiSignalSel[6:0] are for production test purposes only.

15.2.4

Examples of ISO/IEC 14443 A analog and digital test signals

Figure 27

shows a MIFARE card’s answer to a request command using the Q-clock

receiving path. RX reference is given to show the Manchester modulated signal on pin

RX.

The signal is demodulated and amplified in the receiver circuitry. Signal VRXAmpQ is the

amplified side-band signal using the Q-clock for demodulation. The signals VCorrDQ and

VCorrNQ were generated in the correlation circuitry. They are processed further in the

evaluation and digitizer circuitry.

B

C

D

E

F

VEvalR

VTemp

reserved

reserved

reserved

evaluation signal from the right half-bit

temperature voltage derived from band gap

reserved for future use

reserved for future use

reserved for future use

Table 165. Analog test signal selection

…continued

Value

Signal Name

Description

Signal name

Description

s_data

s_valid

data received from the card

when logic 1 is returned the s_data and s_coll signals are

valid

when logic 1 is returned a collision has been detected in the

current bit

internal serial clock:

during transmission, this is the encoder clock

during reception this is the receiver clock

internal synchronized read signal which is derived from the

parallel microprocessor interface

internal synchronized write signal which is derived from the

parallel microprocessor interface

internal 13.56 MHz clock

BPSK output signal

BPSK signal’s amplitude detected

output as defined by the MFOUTSelect register

MFOUTSelect[2:0] bits routed to pin MFOUT

D4h

s_coll

C4h

s_clock

B5h

rd_sync

A5h

wr_sync

96h

83h

E2h

00h

int_clock

BPSK_out

BPSK_sig

no test signal

相關PDF資料 |

PDF描述 |

|---|---|

| MFRX85201HD | Secure contactless reader solution |

| MMBD4148 | High-speed switching diode |

| MMBD6050-V-GS08 | SWITING 70V 0.2A 3PIN SOT-23 - Tape and Reel |

| MMBD6050-V-GS18 | SWITING 70V 0.2A 3PIN SOT-23 - Tape and Reel |

| MMBD7000-V-GS08 | Diode Small Signal Switching 100V 0.2A 3-Pin SOT-23 T/R |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MFRC53101T/0FE,112 | 功能描述:RFID應答器 MIFARE HS READER RoHS:否 制造商:Murata 存儲容量:512 bit 工作溫度范圍:- 40 C to + 85 C 安裝風格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| MFRC53101T/0FE112 | 制造商:NXP Semiconductors 功能描述:CNTCLESS RC 5V ISO14443-A |

| MFRC53101T/0FE112 | 制造商:NXP Semiconductors 功能描述:IC RFID READER 13.56MHZ SOIC-32 |

| MFRC630 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Contactless reader IC |

| MFRC63001HN,518 | 制造商:NXP Semiconductors 功能描述:MFRC63001HN/HVQFN32/REEL13DP// - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。