- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98012 > MC68HC55CD (FREESCALE SEMICONDUCTOR INC) 4 CHANNEL(S), SERIAL COMM CONTROLLER, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HC55CD |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4 CHANNEL(S), SERIAL COMM CONTROLLER, PDSO16 |

| 封裝: | SOIC-16 |

| 文件頁(yè)數(shù): | 15/40頁(yè) |

| 文件大?。?/td> | 284K |

| 代理商: | MC68HC55CD |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

MC68HC55 Technical Data

Technical Data

MC68HC55

22

Functional Description

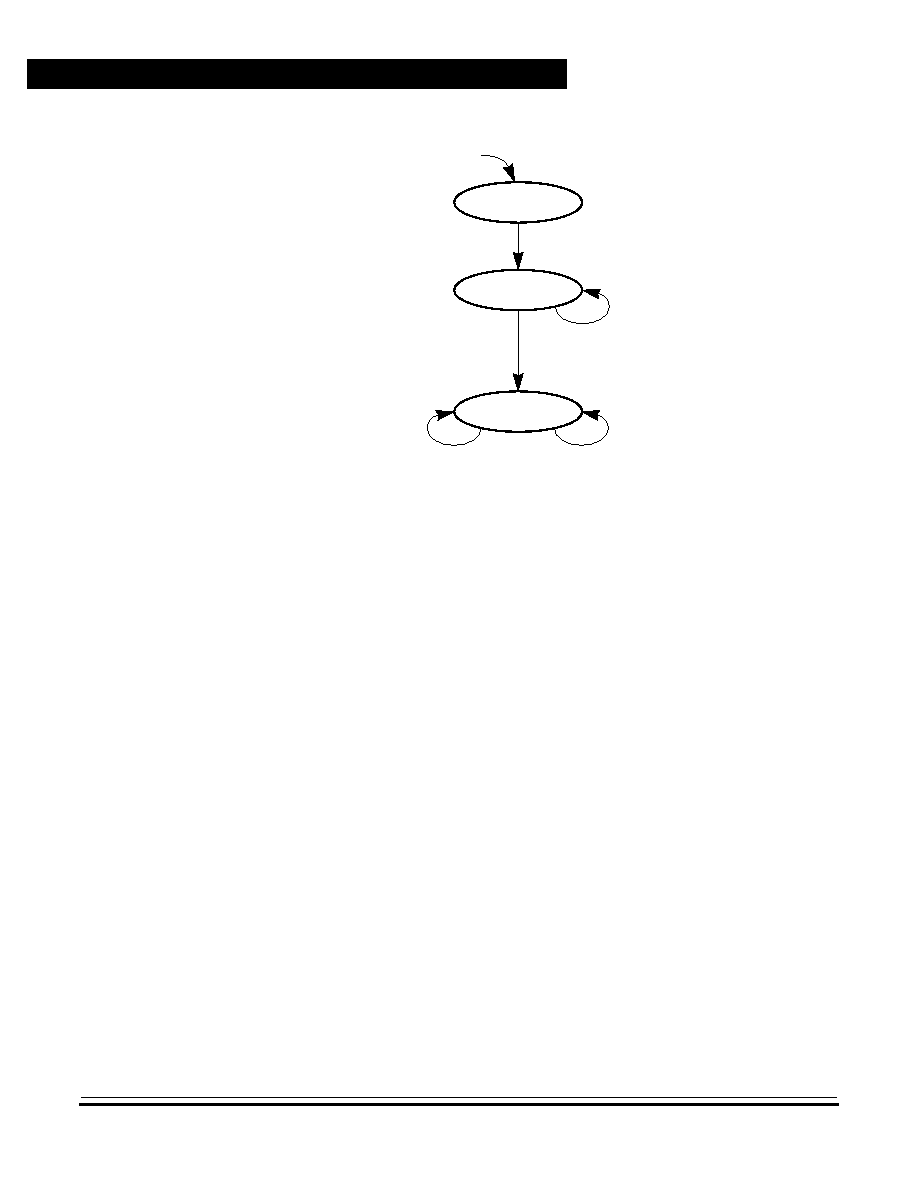

Figure 4-3. State Diagram — SPI Transfer

In the SPI_BURST state, new SPI characters are read-from or

written-to-and-read-from DSI/D registers. If the control register is written,

an ABORT request is generated which will immediately stop any DSI

transfer that was in progress (refer to Figure 4-4). If the DATA register

low byte is written, a transmit FIFO push operation is generated (see

). If the DATA register low byte is accessed (read or written)

and there is at least one entry in the receive FIFO, a receive FIFO pop

operation is generated.

When a DSI transfer results in both an R_FIFO_PUSH and an

X_FIFO_POP, the R_FIFO_PUSH is performed first to avoid the

possibility of the transmit FIFO from getting ahead of the receive FIFO.

describes what happens during DSI serial transfers. State

transfers in this state machine are synchronous with positive edges on

the scaled SCLK and the initial state is WAIT_FRAME_DELAY. Initial

entry into this state is caused by a reset, abort, or by enable becoming

inactive. These conditions cause an asynchronous entry into this state.

The exit to the next state, TRANSFER_DSI_BITS, needs to be

synchronous.

SPI_IDLE

SPI_COMMAND_XFER

SPI_BURST

RESET or CS_INACTIVE/

SPI_WRITE = 0

SPI_BIT_PTR = 7

CS_ACTIVE/

SPI_WRITE = DATA_IN

~LAST_SPI_BIT/

SPI_BIT_PTR = SPI_BIT_PTR – 1

LAST_SPI_BIT/

IF SPI_WRITE & REG_PTR = DATA_L THEN X_FIFO PUSH

REG_PTR = REG_PTR+1 (rolls over 7-0)

IF SPI_WRITE & REG_PTR = CTRL THEN ABORT

LAST_SPI_BIT/

SPI_BIT_PTR = 7;

INITIALIZE REG_PTR FROM COMMAND BITS 2-0

~LAST_SPI_BIT/

SPI_BIT_PTR = SPI_BIT_PTR – 1

SPI_BIT_PTR = 7

IF R_FIFO_NOT_EMPTY & REG_PTR = DATA_L THEN R_FIFO_POP

STATE MACHINE TRANSITIONS

ON RISING EDGES OF SPI CLOCK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC705C4ACFN | 8-BIT, OTPROM, 2.1 MHz, MICROCONTROLLER, PQCC44 |

| MC68HC705C4ACP | 8-BIT, OTPROM, 2.1 MHz, MICROCONTROLLER, PDIP40 |

| MC68HC705C4ACFB | 8-BIT, OTPROM, 2.1 MHz, MICROCONTROLLER, PQFP44 |

| MC68HC705CL4FU | 8-BIT, MROM, 1.84 MHz, MICROCONTROLLER, PQFP80 |

| MC68HC705E1P | 8-BIT, OTPROM, 1 MHz, MICROCONTROLLER, PDIP28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC68T1P | 制造商:Motorola Inc 功能描述: |

| MC68HC705B16CFN | 制造商:Motorola Inc 功能描述: |

| MC68HC705B16FN | 制造商:Rochester Electronics LLC 功能描述: |

| MC68HC705B16NB | 制造商:Rochester Electronics LLC 功能描述: |

| MC68HC705B16NCB | 制造商:Rochester Electronics LLC 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。