- 您現(xiàn)在的位置:買賣IC網 > PDF目錄370643 > HMS30C2000 [Application Specific Solution Product] PDF資料下載

參數(shù)資料

| 型號: | HMS30C2000 |

| 英文描述: | [Application Specific Solution Product] |

| 中文描述: | [專用解決方案產品] |

| 文件頁數(shù): | 71/161頁 |

| 文件大小: | 973K |

| 代理商: | HMS30C2000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁當前第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁

HMS30C7110

2003 MagnaChip Semiconductor Ltd. All Rights Reserved

Version 1.5

71

that some or all of the bits are auto cleared. Base address of Ethernet MAC 1 is 0x1920_1000.

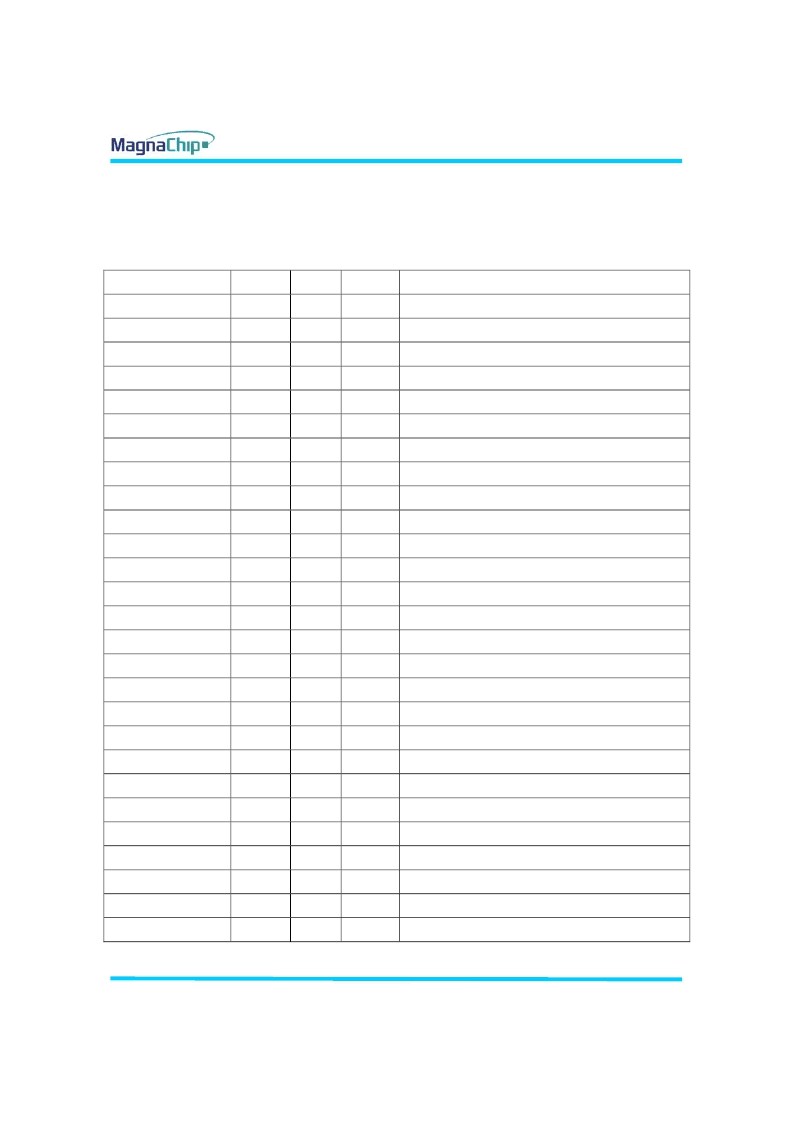

Table 2.22 Registers for Ethernet MAC

Name

Address Width

Access

Description

MAC_MODE

0x00

32

RW

MAC mode register

INT_SRC

0x04

32

RW

Interrupt source register

INT_ENABLE

0x08

32

RW

Interrupt enable register

IF_GAP

0x0C

32

RW

Inter-frame gap register

COLL_CFG

0x10

32

RW

Collision control register

TX_BADDR

0x14

32

RW

Transmit buffer base address

TX_LENGTH

0x18

32

RW

Transmit buffer length

RX_BADDR

0x1C

32

RW

Receive buffer base address

RX_BSTAT

0x20

32

RO

Receive buffer status

RX_BUFLVL

0x24

32

RO

Address/Status buffer level

RX_ADDR_BACK 0x28

32

RO

Receive buffer base address return

CTRL_MODE

0x2C

32

RWC

Control mode register

MII_MODE

0x30

32

RW

MII mode register

MII_CMD

0x34

32

RWC

MII command register

MII_TXDATA

0x38

32

RW

MII transmit data

MII_RXDATA

0x3C

32

RW

MII receive data

RESERVED

0x40

32

Reserved

LENGTH

0x44

32

RW

Max, Min, burst length register

MCAST_ADDR_0 0x48

32

RW

Multicast Address (Most significant)

MCAST_ADDR_1 0x4C

32

RW

Multicast Address (Least significant)

MAC_ADDR_00

0x50

32

RW

MAC address 0 (Most significant 2 bytes)

MAC_ADDR_01

0x54

32

RW

MAC address 0 (Least significant 4 bytes)

MAC_ADDR_10

0x58

32

RW

MAC address 1 (Most significant 2 bytes)

MAC_ADDR_11

0x5C

32

RW

MAC address 1 (Least significant 4 bytes)

MAC_ADDR_20

0x60

32

RW

MAC address 2 (Most significant 2 bytes)

MAC_ADDR_21

0x64

32

RW

MAC address 2 (Least significant 4 bytes)

MAC_ADDR_30

0x68

32

RW

MAC address 3 (Most significant 2 bytes)

相關PDF資料 |

PDF描述 |

|---|---|

| HMS30C7210 | ARM Based 32-Bit Microprocessor |

| HMS30C7080 | Mobile Phone Camera Back-End Processor |

| HMS30C7202 | 32-bit ARM7TDMI RISC static CMOS CPU core |

| HMS30C7202N | Highly-intergrated MPU |

| HMS81C2012A | CMOS Single-Chip 8-Bit Microcontroller with A/D Converter & VFD Driver |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HMS30C7080 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Mobile Phone Camera Back-End Processor |

| HMS30C7110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Multipurpose Network Processor |

| HMS30C7202 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:32-bit ARM7TDMI RISC static CMOS CPU core |

| HMS30C7202N | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Highly-intergrated MPU |

| HMS30C7210 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ARM Based 32-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復。