- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370499 > HDMP-1032 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) PDF資料下載

參數(shù)資料

| 型號(hào): | HDMP-1032 |

| 英文描述: | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| 中文描述: | 1.4 GBd發(fā)射機(jī)芯片組與CIMT編碼器/解碼器和可變數(shù)據(jù)速率(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd傳送器) |

| 文件頁(yè)數(shù): | 6/32頁(yè) |

| 文件大?。?/td> | 346K |

| 代理商: | HDMP-1032 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

6

Sign

The sign circuitry determines the

disparity of the encoded word.

Disparity is defined as the total

number of high bits minus the

total number of low bits.

Accumulator Block

This block is responsible for

keeping track of total disparity

of all previously sent words.

Invert Block

The Invert block is responsible

for maintaining the DC balance

of the serial line. It determines

based on history and the sign

of the current encoded word

whether the current encoded

word should be inverted to

bring the serial line closer to

the desired 50% duty cycle.

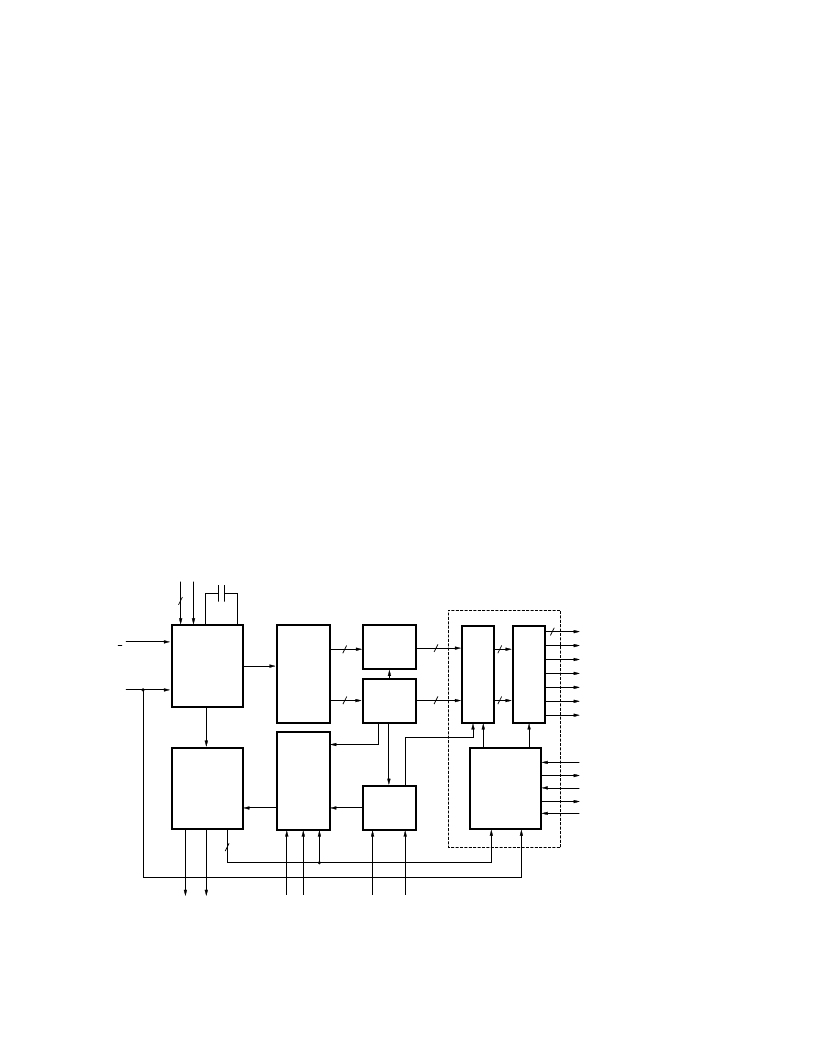

HDMP-1034 Rx Block Diagram

The HDMP-1034 receiver was

designed to convert a serial data

signal sent from the HDMP-1032

into either 16 or 17 bit wide

parallel data. The HDMP-1034

performs the following functions:

Frequency Lock

Phase Lock

Encoded Word Synchronization

De-multiplexing

Word Decoding

Encoding Error Detection

Input Sampler and Clock-Data

Recovery (CDR)

In order to compensate for any

amplitude distortion present in

the serial data signal, the high-

speed inputs, HSIN

±

, are always

equalized. The CDR block locks

to the frequency of the REFCLK

and to the phase of the sampled

input signal. The recovered

data is sent to the DEMUX block

and a bit-rate clock is sent to

the Clock Generator block. If

the serial data signal is absent,

the CDR block will maintain

frequency lock onto REFCLK.

Figure 4. HDMP-1034 Receiver Block Diagram.

The RXDIV1/0 pins select the

data rate range by dividing the

VCO range by 1, 2 or 4. When

RXDIV1/0 = 1/1, the internal

VCO is bypassed and the test

clock input TSTCLK can be

used as the serial input.

Clock Generator

Using the recovered bit-rate

clock, the CLOCK GENERATOR

block generates all of the re-

quired internal clocks including

the word rate clocks: RXCLK0/1.

Using the WORD ALIGN block’s

bit adjust output, the phase of

the word-rate clocks is adjusted

bit by bit for proper word align-

ment. For testing purposes

this adjustment function can be

disabled using the WSYNCDSB

input; word alignment can also

be forced using the #RESET pin.

RXREADY

RXERROR

RXDATA

RXCNTL

RXDSLIP

WORD

ALIGN

SYNC

LOGIC

SHFOUT

SRQIN

SRQOUT

PASSENB

O

D

RXFLAG

RX[0-15]

SHFIN

INVERT

DECODE

FLAG

DESCRM

HSIN

R

E

CLOCK

GENERATOR

DEMUX

CDR

RXCLK0/1

#

W

REFCLK

R

PASS SYSTEM

RXCAP1/0

T

+

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

| HDMP-1514 | Fibre Channel Receiver Chipset(光纖通道接收芯片) |

| HDMP-1526 | Transistor Diode Kit;Contents Of Kit:Transistor/Diode Kit |

| HDMP-1536 | Fibre Channel Transceiver Chip |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1032A | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱(chēng):AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034A | 制造商:HP 制造商全稱(chēng):Agilent(Hewlett-Packard) 功能描述:Transmitter/Receiver Chip Set |

| HDMP-1512 | 制造商:AGILENT 制造商全稱(chēng):AGILENT 功能描述:Fibre Channel Transmitter and Receiver Chipset |

| HDMP-1514 | 制造商:AGILENT 制造商全稱(chēng):AGILENT 功能描述:Fibre Channel Transmitter and Receiver Chipset |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。