- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383967 > TSB82AA2I (Texas Instruments, Inc.) 1394b OHCI-LYNX CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | TSB82AA2I |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 1394b OHCI-LYNX CONTROLLER |

| 中文描述: | 的1394b OHCI的山貓控制器 |

| 文件頁數(shù): | 64/104頁 |

| 文件大小: | 461K |

| 代理商: | TSB82AA2I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁當(dāng)前第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁

422

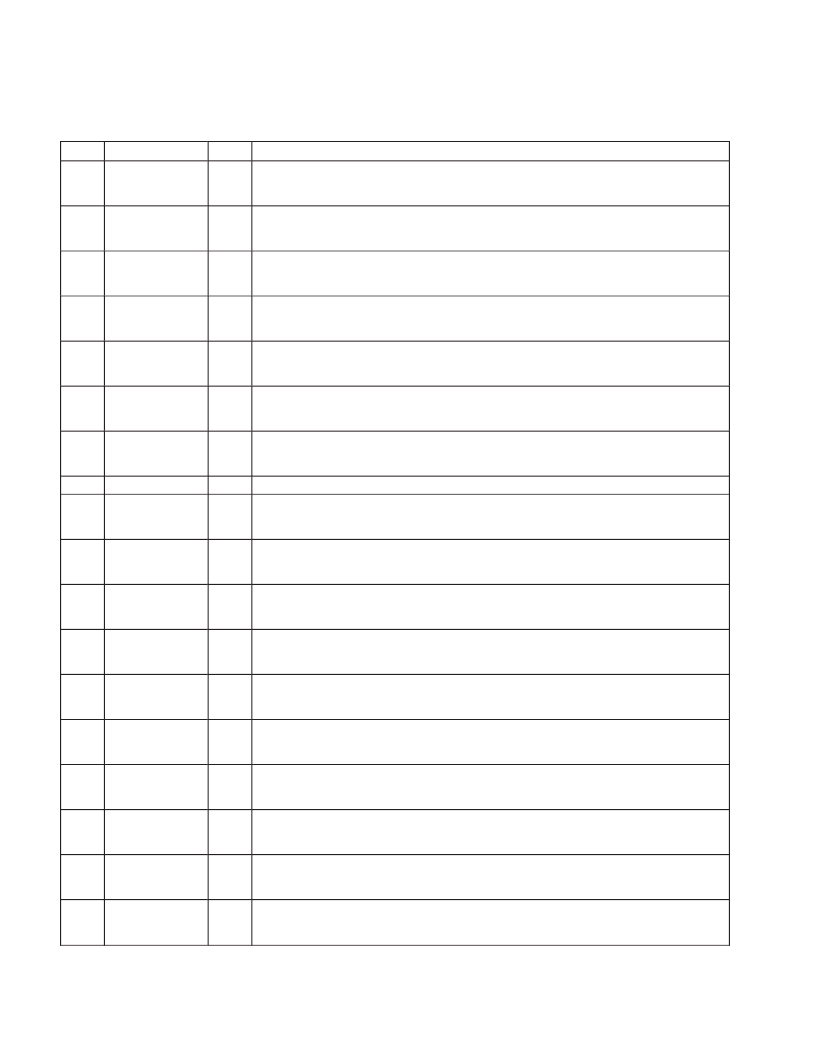

Table 417. Interrupt Mask Register Description (Continued)

BIT

FIELD NAME

TYPE

DESCRIPTION

21

cycle64Seconds

RSC

When this bit and bit 21 (cycle64Seconds) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this 64-second-cycle interrupt mask enables

interrupt generation.

20

cycleSynch

RSC

When this bit and bit 20 (cycleSynch) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this isochronous-cycle interrupt mask enables

interrupt generation.

19

phy

RSC

When this bit and bit 19 (phy) in the interrupt event register at OHCI offset 80h/84h (see Section 4.21,

Interrupt Event Register

) are set to 1, this PHY-status-transfer interrupt mask enables interrupt

generation.

18

regAccessFail

RSC

When this bit and bit 18 (regAccessFail) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this register-access-failed interrupt mask enables

interrupt generation.

17

busReset

RSC

When this bit and bit 17 (busReset) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this bus-reset interrupt mask enables interrupt

generation.

16

selfIDcomplete

RSC

When this bit and bit 16 (selfIDcomplete) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this self-ID-complete interrupt mask enables

interrupt generation.

15

selfIDcomplete2

RSC

When this bit and bit 15 (selfIDcomplete2) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this second-self-ID-complete interrupt mask

enables interrupt generation.

1410

RSVD

R

Reserved. Bits 1410 return 0s when read.

9

lockRespErr

RSC

When this bit and bit 9 (lockRespErr) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this lock-response-error interrupt mask enables

interrupt generation.

8

postedWriteErr

RSC

When this bit and bit 8 (postedWriteErr) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this posted-write-error interrupt mask enables

interrupt generation.

7

isochRx

RSC

When this bit and bit 7 (isochRx) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this isochronous-receive-DMA interrupt mask

enables interrupt generation.

6

isochTx

RSC

When this bit and bit 6 (isochTx) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this isochronous-transmit-DMA interrupt mask

enables interrupt generation.

5

RSPkt

RSC

When this bit and bit 5 (RSPkt) in the interrupt event register at OHCI offset 80h/84h (see Section 4.21,

Interrupt Event Register

) are set to 1, this receive-response-packet interrupt mask enables interrupt

generation.

4

RQPkt

RSC

When this bit and bit 4 (RQPkt) in the interrupt event register at OHCI offset 80h/84h (see Section 4.21,

Interrupt Event Register

) are set to 1, this receive-request-packet interrupt mask enables interrupt

generation.

3

ARRS

RSC

When this bit and bit 3 (ARRS) in the interrupt event register at OHCI offset 80h/84h (see Section 4.21,

Interrupt Event Register

) are set to 1, this asynchronous-receive-response-DMA interrupt mask

enables interrupt generation.

2

ARRQ

RSC

When this bit and bit 2 (ARRQ) in the interrupt event register at OHCI offset 80h/84h (see Section 4.21,

Interrupt Event Register

) are set to 1, this asynchronous-receive-request-DMA interrupt mask enables

interrupt generation.

1

respTxComplete

RSC

When this bit and bit 1 (respTxComplete) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this response-transmit-complete interrupt mask

enables interrupt generation.

0

reqTxComplete

RSC

When this bit and bit 0 (reqTxComplete) in the interrupt event register at OHCI offset 80h/84h (see

Section 4.21,

Interrupt Event Register

) are set to 1, this request-transmit-complete interrupt mask

enables interrupt generation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSC2200EVM | TSC2200 Touch Screen Controller Evaluation Module(TSC2200觸摸屏控制器評估模塊) |

| TSC427CBA | Dual Power MOSFET Drivers |

| TSC427CPA | Dual Power MOSFET Drivers |

| TSC428CBA | Dual Power MOSFET Drivers |

| TSC426CBA | Dual Power MOSFET Drivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB82AA2IPGE | 功能描述:接口 - 專用 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| TSB82AA2IPGEEP | 功能描述:1394 接口集成電路 Mil Enh 1394b OHCI- Lynx Cntrlr RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2PGE | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2PGEG4 | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB82AA2ZGW | 功能描述:1394 接口集成電路 OHCI-Lynx Controller RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。