- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383644 > MT90500 (Mitel Networks Corporation) Multi-Channel ATM AAL1 SAR(多通道 ATM AAL1分段及重組設(shè)備(基于通訊總線的系統(tǒng)與ATM網(wǎng)絡(luò)的接口)) PDF資料下載

參數(shù)資料

| 型號: | MT90500 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Multi-Channel ATM AAL1 SAR(多通道 ATM AAL1分段及重組設(shè)備(基于通訊總線的系統(tǒng)與ATM網(wǎng)絡(luò)的接口)) |

| 中文描述: | 多通道自動柜員機(jī)AAL1特區(qū)(多通道自動柜員機(jī)AAL1分段及重組設(shè)備(基于通訊總線的系統(tǒng)與空中交通管理網(wǎng)絡(luò)的接口)) |

| 文件頁數(shù): | 138/159頁 |

| 文件大?。?/td> | 514K |

| 代理商: | MT90500 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁當(dāng)前第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁

MT90500

138

The MT90500 will work with a variety of standard Synchronous SRAM parts. The burst feature of the

Synchronous SRAM is not used by the MT90500, and since the SSRAM is not connected to a cache controller,

some of the control pins of most SSRAMS are not used by the MT90500. The common control pin names for

the SSRAM, and their connections when used with the MT90500, are listed in Table 98, and Table 99.

The Secondary UTOPIA bus of the MT90500, and the Transmit UTOPIA multiplexer, allow application flexibility

in working with a variety of off-the-shelf data SARs. This feature also allows two MT90500s to be combined for

a full 2048 full-duplex TDM channel application (allowing full connection to a 4096 channel backplane). Note

that each MT90500 carries 1024 channels in each direction, not 2048 transmitted by one MT90500, and 2048

received by the other MT90500. The capabilities of the TX SAR and RX SAR internal blocks are balanced at

1024 channels.

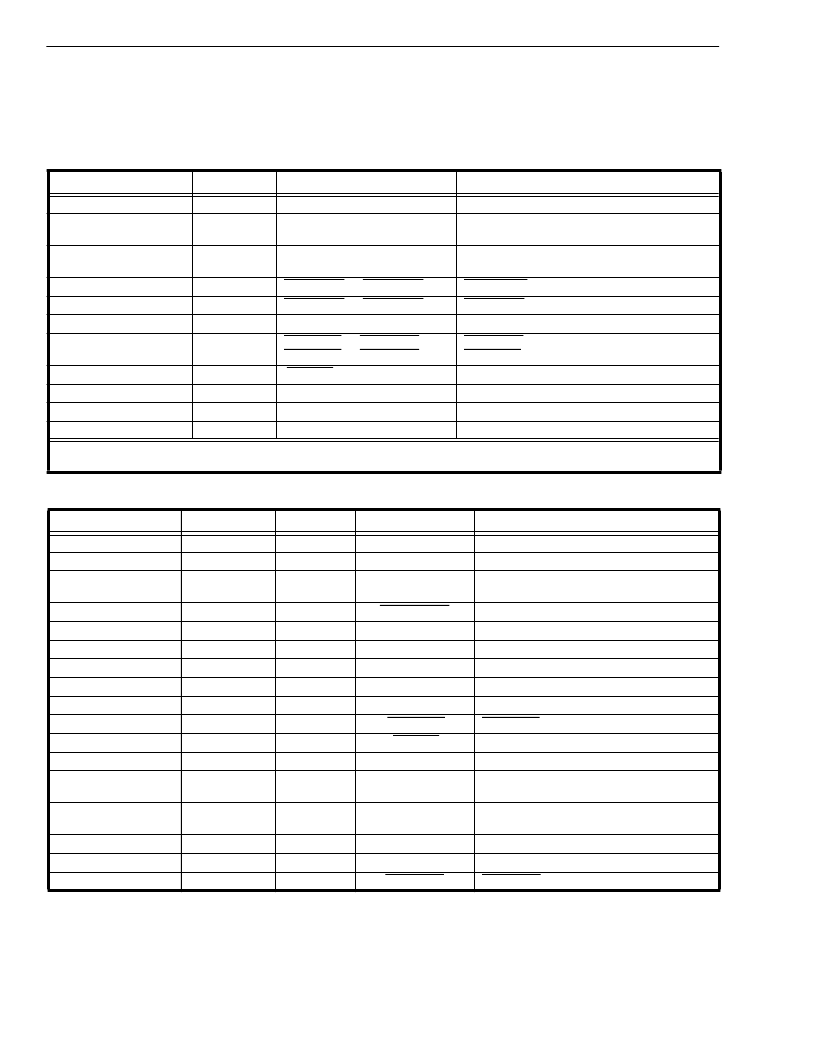

Table 98 - MT90500 Connections to 18-bit Synchronous SRAM

Pin Function

SSRAM

MT90500

Notes

Address

A0-A14

MEM_ADD[14:0]

Data

DQ[0:7, 9:16]

MEM_DAT[15:0], or

MEM_DAT[31:16]

MEM_DAT[31:16] used for second SSRAM chip.

Underrun Flag

DQ[8, 17]

MEM_PAR[1:0], or

MEM_PAR[3:2]

MEM_PAR[3:2] used for second SSRAM chip.

Lower Byte Write Enable

LW*

MEM_WR[0], or MEM_WR[2]

MEM_WR[2] used for second SSRAM chip.

Upper Byte Write Enable

UW*

MEM_WR[1], or MEM_WR[3]

MEM_WR[3] used for second SSRAM chip.

Memory Clock

K

MEMCLK

Chip Enable

E*

MEM_CS0L, or MEM_CS0H, or

MEM_CS1L, or MEM_CS1H

MEM_CS0H used for second SSRAM chip.

MEM_CS1x used for second bank of SSRAM chips.

Output Enable

G*

MEM_OE

Burst Address Advance

ADV*

-

Never enabled - pull to VDD to disable

Processor Address Status

ADSP*

-

Never enabled - pull to VDD to disable

Controller Address Status

ADSC*

-

Always enabled - tie to GND to enable

Note:

The pin names in this table correspond to those for the Motorola 32K x 18-bit BurstRAM Synchronous Fast Static RAM

(MCM67H518).

Table 99 - MT90500 Connections to 32/36-bit Synchronous SRAM

Pin Function

MCM69F536A

CY7C1329

MT90500

Notes

Address

SA

A

MEM_ADD

Data

DQ

DQ[31:0]

MEM_DAT[31:0]

Underrun Flag

DQ8[d:a]

(pull-up)

MEM_PAR[3:0]

If TDM Underrun Error indication not used, pull-

up MEM_PAR[3:0] to V

DD3

.

Byte Write

SB*[d:a]

BW*[3:0]

MEM_WR[3:0]

Global Write

SGW*

GW*

-

Tie high (disable global writes)

Byte Write Enable

SW*

BWE*

-

Tie low (enable byte-writes)

Clock

K

CLK

MEMCLK

Chip Enable 1

SE1*

CE1*

-

Tie low (enable)

Chip Enable 2

SE2

CE2

-

Tie high (enable)

Chip Enable 3

SE3*

CE3*

MEM_CS0L

MEM_CS1L used for second bank/ chip.

Output Enable

G*

OE*

MEM_OE

Burst Address Advance

ADV*

ADV*

-

Tie high (disable)

Processor Address

Status

ADSP*

ADSP*

-

Tie high (disable)

Controller Address

Status

ADSC*

ADSC*

-

Tie low (enable)

Sleep

-

ZZ

-

Tie low

Burst Mode

LBO*

MODE

-

Tie low or tie high

no connect

-

-

MEM_CSxH

MEM_CSxH not used with 32/36 bit memory

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90500 | Multi-Channel ATM AAL1 SAR |

| MT90500AL | Multi-Channel ATM AAL1 SAR |

| MT90502 | Multi-Channel AAL2 SAR(多通道 ATM AAL2分段及重組設(shè)備(基于通訊總線的系統(tǒng)與ATM網(wǎng)絡(luò)的接口)) |

| MT90732AP | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| MT90732 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90500AL | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Multi-Channel ATM AAL1 SAR |

| MT90500AL-ENG1 | 制造商:Mitel Networks Corporation 功能描述: |

| MT90502 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-Channel AAL2 SAR |

| MT90502_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Multi-Channel AAL2 SAR |

| MT90502AG | 制造商:Rochester Electronics LLC 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。