- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45052 > M66596WG UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 PDF資料下載

參數(shù)資料

| 型號(hào): | M66596WG |

| 元件分類: | 總線控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| 封裝: | 0.80 MM PITCH, FBGA-64 |

| 文件頁(yè)數(shù): | 66/133頁(yè) |

| 文件大小: | 1611K |

| 代理商: | M66596WG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)當(dāng)前第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)

M66596FP/WG

rev .1.00

2006.3.14

page 36 of 127

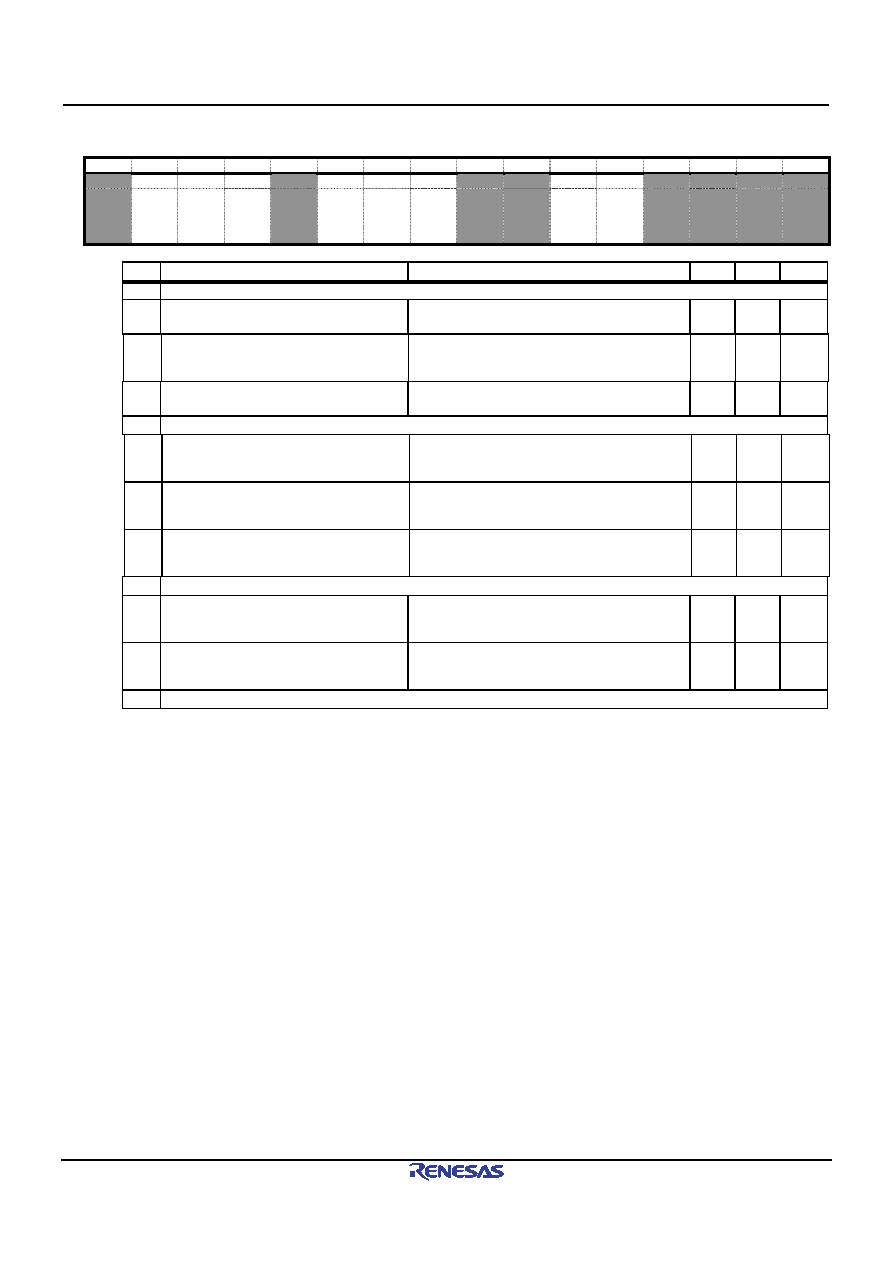

Interrupt status register 1[INTSTS1]

<Address: 42H>

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

BCHG

SOFR

DTCH

BEMP

NRDY

BRDY

SIGN

SACK

?

0

-

0

-

0

-

0

?

0

-

0

-

0

-

0

?

0

-

0

-

0

?

Bit

Name

Function

S/W

H/W

Note

15 Nothing is placed here. These should be fixed at “0”.

14 BCHG

USB bus change interrupt status

0: BCHG Interrupts not issued

1: BCHG Interrupts issued

R/W

W

13 SOFR

Frame number refresh interrupt status

This bit is a mirror bit of a 40H SOFR bit.

0: SOF Interrupts not issued

1: SOF Interrupts issued

R/W(0)

W

2.9.1

12 DTCH

Full-Speed detach detect interrupt status

0: DTCH Interrupts not issued

1: DTCH Interrupts issued

R/W

W

11 Nothing is placed here. This should be fixed at “0”.

10 BEMP

Buffer Empty interrupt status

This bit is a mirror bit of a 40H BEMP bit.

0: BEMP interrupts not issued

1: BEMP interrupts issued

R

W

2.9.1

9

NRDY

Buffer Not Ready response interrupt

status

This bit is a mirror bit of a 40H NRDY bit.

0: NRDY interrupts not issued

1: NRDY interrupts issued

R

W

2.9.1

8

BRDY

Buffer Ready interrupt status

This bit is a mirror bit of a 40H BRDY bit.

0: BRDY interrupts not issued

1: BRDY interrupts issued

R

W

2.9.1

7-6 Nothing is placed here. This should be fixed at “0”.

5

SIGN

Setup transaction error detect interrupt

status

0: SIGN interrupts not issued

1: SIGN interrupts issued

R/W

R

4

SACK

Setup transaction complete interrupt

status

0: SACK interrupts not issued

1: SACK interrupts issued

R/W

R

3-0 Nothing is placed here. This should be fixed at “0”.

<<Notes>>

*4) DTCH, SIGN, SACK bit are effective only at the time of a Host mode.

*5) The DTCH bit is effective only at the time of Full-Speed mode.

Please perform detach detection by S/W, such as detecting ignore packet from peripheral device at the time of

Hi-Speed mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M6XXLFXI | OTHER CLOCK GENERATOR, QCC16 |

| M300LFXIT | 50 MHz, OTHER CLOCK GENERATOR, QCC16 |

| M74HC00C1R | HC/UH SERIES, QUAD 2-INPUT NAND GATE, PQCC20 |

| M74HC157B1N | HC/UH SERIES, QUAD 2 LINE TO 1 LINE MULTIPLEXER, TRUE OUTPUT, PDIP16 |

| M74HC158C1 | HC/UH SERIES, QUAD 2 LINE TO 1 LINE MULTIPLEXER, INVERTED OUTPUT, PQCC20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M66596WG#RB0Z | 制造商:Renesas Electronics 功能描述:Tray 制造商:Renesas 功能描述:0 |

| M6668 | 制造商:Tamura Corporation of America 功能描述: |

| M66700P | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:DUAL HIGH-SPEED CCD CLOCK DRIVER |

| M66700WP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:DUAL HIGH-SPEED CCD CLOCK DRIVER |

| M66701P | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:DUAL HIGH-SPEED CCD CLOCK DRIVER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。