- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385387 > HM17CM256 (HYNIX SEMICONDUCTOR INC) 128XRGBX82 OUTPUT LCD DRIVER IC with built-in RAM PDF資料下載

參數(shù)資料

| 型號: | HM17CM256 |

| 廠商: | HYNIX SEMICONDUCTOR INC |

| 元件分類: | 顯示驅(qū)動器 |

| 英文描述: | 128XRGBX82 OUTPUT LCD DRIVER IC with built-in RAM |

| 中文描述: | LIQUID CRYSTAL DISPLAY DRIVER, UUC580 |

| 封裝: | 19.75 X 2.39 MM, GOLD BUMP, DIE-580 |

| 文件頁數(shù): | 32/111頁 |

| 文件大?。?/td> | 2094K |

| 代理商: | HM17CM256 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁

HM17CM256

- 32 -

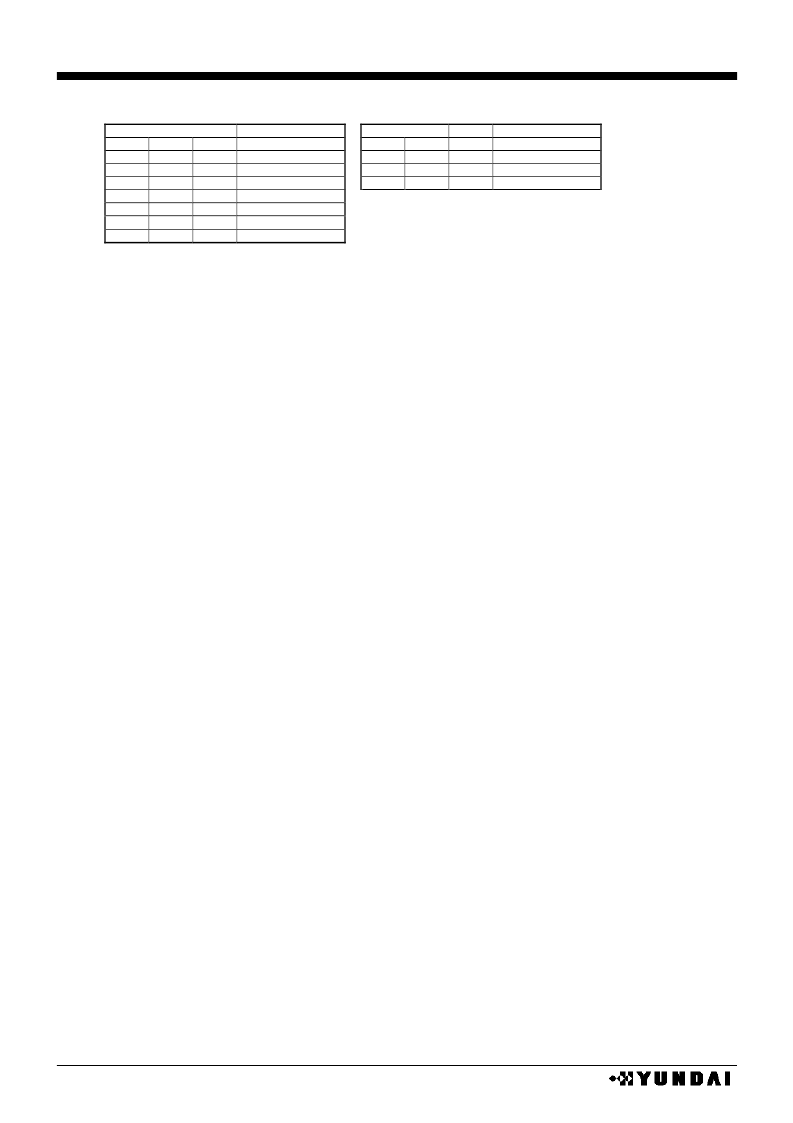

gradation level table (MON=”1”, Black & white mode)

(MSB)RAM data (LSB)

Gradation level

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

RAM data

0

0

1

1

* : Don’t Care

GLSB

*

*

*

*

Gradation level

0

0

1

1

0

0

0

0

1

1

1

1

0

1

0

1

(12) GRADATION LSB CONTROL

At 256 colors input mode, this IC provides segment driver output for 8-gradation display using

successive 3 bits of data and that for 4-gradation display using successive 2 bits of data.

The segment driver output for the 4-gradation display uses 2 bits written to the corresponding RAM

area and 1 bit supplemented by the gradation LSB circuit, and then selects 4 gradations from 8-

gradations.

At fixed gradation mode, the segment driver output for the 4-gradation display result in a gradation

level of 0 regardless of gradation LSB register, when 2 bits of data on the display RAM are “00”.

When 2 bits of data on the display RAM is “11”, a gradation level of 7/7 is selected regardless of

gradation LSB register. The other gradation levels are selected depending on 2 bits of data on the

display RAM and the gradation LSB register.

One bit of data is supplemented by setting the gradation LSB register (GLSB).

For this register, the bit information specified for only one time setting is used as the LSB of the

RAM for all the 4-gradation segment drivers.

Gradation LSB = “0”: Set 0 as the LSB of the RAM for 4-gradation segment drivers.

Gradation LSB = “1”: Set 1 as the LSB of the RAM for 4-gradation segment drivers.

(13) GRADATION PALETTE

This IC has two gradation display modes, the fixed gradation display mode and the variable

gradation display mode.

Select mode by setting the gradation display mode register (PWM command) to the purpose.

PWM=”0” : variable gradation mode among 32-level gradations.

PWM=”1” : fixed 8 gradation mode

To select the best gradation level suited to LCD panel at variable gradation display mode, use the

gradation palette register among 32-level gradation palettes. Segment driver outputs are set by

selected 8-level gradation palette.

The gradation palette register provides three registers ( palette Aj, Bj, and Cj : j=0

~

7 ) for the

segment driver outputs, SEGAi(0

~

127), SEGBi(0

~

127), and SEGCi(0

~

127) . Each register

consists of a 5-bit register, selecting 8 gradations from the 32 gradation pattern.

Segment driver selects 4 gradations among 8 gradation by 2 bits wrote-in RAM and 1bit calibrated

by GLSB.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HM202N10 | 2,000V - 4,000V Miniature Hybrid Multiplier |

| HM202N8 | 2,000V - 4,000V Miniature Hybrid Multiplier |

| HM202P08 | 2,000V - 4,000V Miniature Hybrid Multiplier |

| HM202P10 | 2,000V - 4,000V Miniature Hybrid Multiplier |

| HM202P8 | 2,000V - 4,000V Miniature Hybrid Multiplier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HM17CM4096 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:128XRGBX162 OUTPUT LCD DRIVER IC with built-in RAM |

| HM18 | 制造商:BITECH 制造商全稱:Bi technologies 功能描述:Common-Mode Chokes |

| HM180K | 制造商:Ohmite Mfg Co 功能描述: |

| HM18-10001 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EE Style Common-Mode Chokes |

| HM18-10002 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EE Style Common-Mode Chokes |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。