- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371670 > 83C795 (SMSC Corporation) Ethernet System Controller PDF資料下載

參數(shù)資料

| 型號: | 83C795 |

| 廠商: | SMSC Corporation |

| 英文描述: | Ethernet System Controller |

| 中文描述: | 以太網(wǎng)系統(tǒng)控制器 |

| 文件頁數(shù): | 33/136頁 |

| 文件大小: | 1996K |

| 代理商: | 83C795 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁

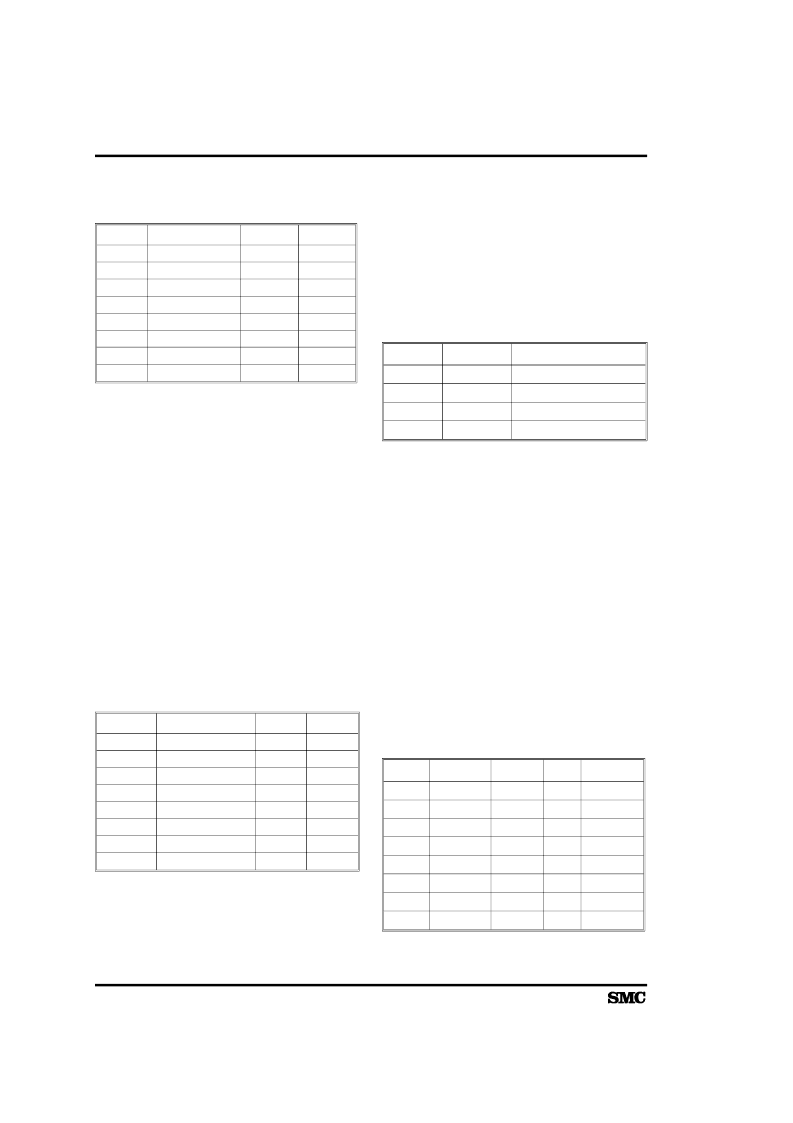

BIT

IAR

RESET

0

0

0

0

1

0

0

0

INIT

7

6

5

4

3

2

1

0

IA15

IA14

IA13

IA8

IA7

IA6

IA5

PNPBOOT

0

0

0

0

1

0

0

0

Bits 7-5: IA15-IA13

, I/O Address Lines

These bits are compared against the A15-A13 lines

from the host when IOR or IOW are active and AEN

is not. To access the chip, the lines must match.

Bits 4-1: IA8-IA5

, I/O Address Lines

These bits are compared against the A8-5 lines

from the host when IOR or IOW are active and AEN

is not. To access the chip, the lines must match.

Bit 0: PNPBOOT,

Plug and Play Boot Bit

PNPBOOT = 1 to indicate to the Plug and Play

hardware that the adapter is a boot card. This

allows the 83C795 address decoders to be active

without waiting for the Plug and Play hardware

activate command.

5.1.14 RAR - RAM Address Register

Read/Write Port = OB SWH=1

This register controls the base address and window

size for the buffer RAM.

BIT

RAR

RESET

0

0

0

0

0

1

0

0

INIT

7

6

5

4

3

2

1

0

HRAM

RA17

RAMSZ1

RAMSZ0

RA16

RA15

RA14

RA13

0

0

0

0

0

1

0

0

Bit 7: HRAM

, High RAM Address

This bit provides a means of locating the buffer

memory above the 1MB DOS limit. When HRAM =

0, the buffer address decoder matches LA23-LA20

against zero. When HRAM = 1, the LA23-LA20

lines are matched against the value F. This field is

not supported by the Plug and Play hardware.

Bits 5-4: RAMSZ1-RAMSZ0

, Buffer Window Size

Field

This encoded field determines the apparent size of

the buffer RAM. It is decoded in the following man-

ner:

SZ1

SZ0

Window Size

8K Bytes

16K Bytes

32K Bytes

64K Bytes

0

0

1

1

0

1

0

1

TABLE 5-5. BUFFER WINDOW SIZE FIELD

Bits 6, 3-0: RA17, RA16-RA13

, RAM Base

Address Field

These bits form part of the base address for the

buffer RAM decoder along with the fixed value of

’11’ for RA19-RA18. When SA19-SA13 has a value

between this base address and the base plus the

window size, the request for memory is recognized.

Once the SA19-SA13 value is no longer in this

range, the host ends the access.

Note

The 64K window size is not supported

by Plug and Play.

5.1.15 BIO - ROM Control Register

Read/Write Port = 0C SWH = 1

This register programs the base address and

window size for the external ROM.

BIT

7

6

5

4

3

2

1

0

BIO

RESET

0

0

1

1

0

0

0

0

INIT

0

0

1

1

0

0

0

0

RECALL

EE

EE

EE

EE

EE

EE

EE

EE

FINE16

BA17

BIOSZ1

BIOSZ0

BA16

BA15

BA14

BA13

83C795

ETHERNET SYSTEM CONTROLLER REGISTERS

20

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 84063 | The Constituents of Semiconductor Components |

| 8406601QA | CMOS Programmable Peripheral Interface |

| 8406601XA | CMOS Programmable Peripheral Interface |

| 8406602XA | CMOS Programmable Peripheral Interface |

| 8406602QA | CMOS Programmable Peripheral Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 83C800-009 | 制造商:DRS 功能描述: |

| 83C825EQFP | 制造商:SMSC 功能描述: |

| 83C845 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Microcontrollers for TV and video MTV |

| 83C851 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:CMOS single-chip 8-bit microcontroller with on-chip EEPROM |

| 83C852DIE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。