- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225535 > W942504CH-7 (WINBOND ELECTRONICS CORP) 64M X 4 DDR DRAM, 0.75 ns, PDSO66 PDF資料下載

參數(shù)資料

| 型號(hào): | W942504CH-7 |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類: | DRAM |

| 英文描述: | 64M X 4 DDR DRAM, 0.75 ns, PDSO66 |

| 封裝: | 0.400 X 0.875 INCH, 0.65 MM PITCH, TSOP2-66 |

| 文件頁數(shù): | 4/45頁 |

| 文件大小: | 1261K |

| 代理商: | W942504CH-7 |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

W942504CH

- 12 -

(8)

VTT is not applied directly to the device. VTT is a system supply for signal termination resistors, is expected to be set

equal to VREF and must track variations in the DC level of VREF.

(9)

These parameters depend on the output loading. Specified values are obtained with the output open.

(10) Transition times are measured between VIH min(AC) and VIL max(AC).Transition (rise and fall) of input signals have a

fixed slope.

(11) IF the result of nominal calculation with regard to tCK contains more than one decimal place, the result is rounded up to

the nearest decimal place.

(i.e., tDQSS = 0.75

× tCK, tCK = 7.5 nS, 0.75 × 7.5 ns = 5.625 ns is rounded up to 5.6 nS.)

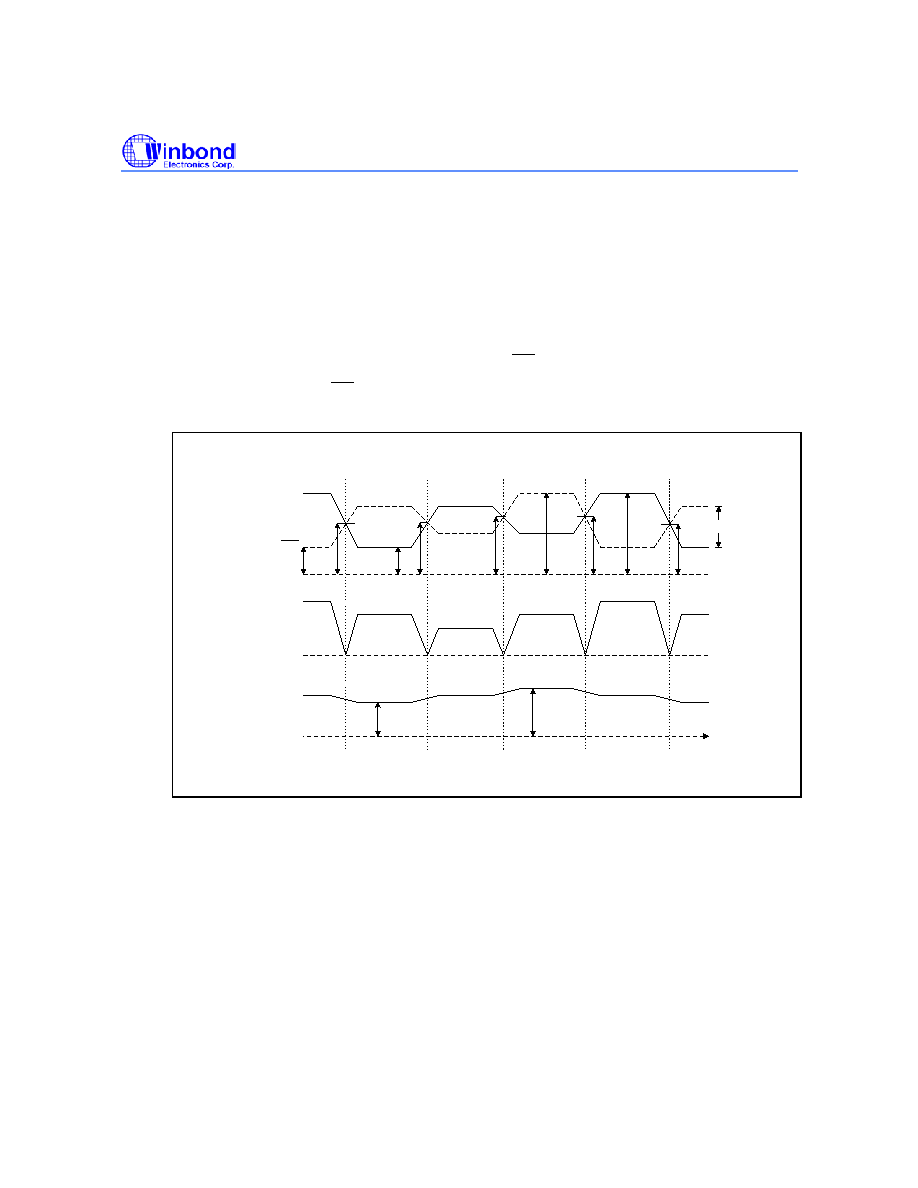

(12) VX is the differential clock cross point voltage where input timing measurement is referenced.

(13) VID is magnitude of the difference between CLK input level and CLK input level.

(14) VISO means {VICK(CLK)+VICK( CLK )}/2.

(15) Refer to the figure below.

CLK

VSS

VICK

VX

VICK

VID(AC)

0 V Differential

VISO

VISO(min)

VISO(max)

VSS

(16) tAC and tDQSCK depend on the clock jitter. These timing are measured at stable clock.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W9864G6IH-6 | 4M X 16 DDR DRAM, 5 ns, PDSO54 |

| WA-1RX33-A4 | SNAP ACTING/LIMIT SWITCH |

| WA-A325CBM | Peripheral Interface |

| WA-A325CPC | Peripheral Interface |

| WA-A325CPI | Peripheral Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W942508BH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM |

| W942508CH | 制造商:WINBOND 制造商全稱:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM |

| W942508CH-5 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM |

| W942508CH-6 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM |

| W942508CH-7 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。