- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225535 > W942504CH-7 (WINBOND ELECTRONICS CORP) 64M X 4 DDR DRAM, 0.75 ns, PDSO66 PDF資料下載

參數(shù)資料

| 型號(hào): | W942504CH-7 |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類: | DRAM |

| 英文描述: | 64M X 4 DDR DRAM, 0.75 ns, PDSO66 |

| 封裝: | 0.400 X 0.875 INCH, 0.65 MM PITCH, TSOP2-66 |

| 文件頁數(shù): | 17/45頁 |

| 文件大小: | 1261K |

| 代理商: | W942504CH-7 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

W942504CH

- 24 -

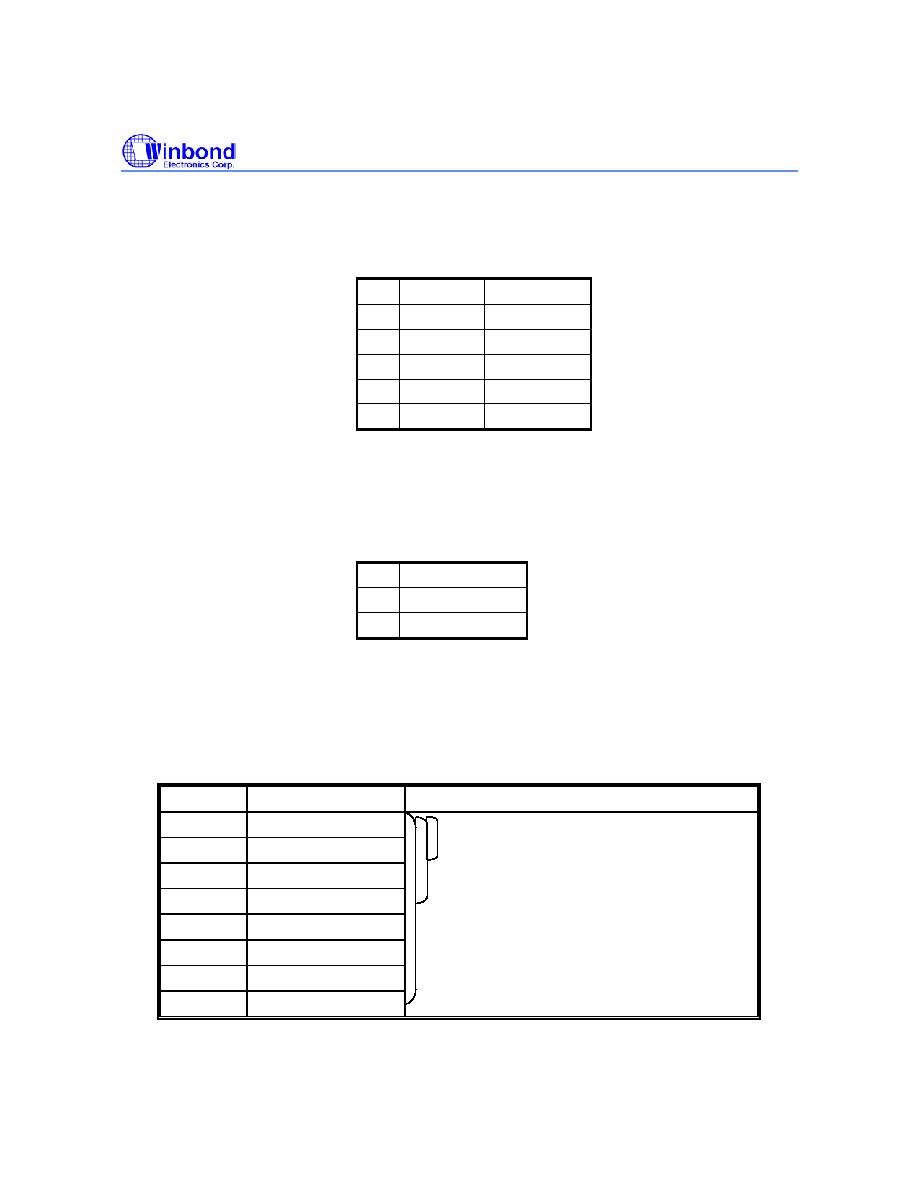

1. Burst Length field (A2 to A0)

This field specifies the data length for column access using the A2 to A0 pins and sets the Burst

Length to be 2, 4, and 8 words.

A2

A1

A0

Burst Length

0

Reserved

0

1

2 words

0

1

0

4 words

0

1

8 words

1

x

Reserved

2. Addressing Mode Select (A3)

The Addressing Mode can be one of two modes; Interleave mode or Sequential Mode, When the

A3 bit is "0", Sequential mode is selected. When the A3 bit is "1", Interleave mode is selected. Both

addressing Mode support burst length 2, 4, and 8 words.

A3

Addressing mode

0

Sequential

0

Interleave

Address sequence of Sequential mode

A column access is performed by incrementing the column address input to the device. The

address is varied by the Burst Length as the following.

Addressing Sequence of Sequential Mode

DATA

ACCESS ADDRESS

BURST LENGTH

Data 0

n

2 words (address bits is A0)

Data 1

n + 1

not carried from A0 to A1

Data 2

n + 2

4 words (address bit A0, A1)

Data 3

n + 3

not carried from A1 to A2

Data 4

n + 4

Data 5

n + 5

8 words(address bits A2, A1 and A0)

Data 6

n + 6

not carried from A2 to A3

Data 7

n + 7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W9864G6IH-6 | 4M X 16 DDR DRAM, 5 ns, PDSO54 |

| WA-1RX33-A4 | SNAP ACTING/LIMIT SWITCH |

| WA-A325CBM | Peripheral Interface |

| WA-A325CPC | Peripheral Interface |

| WA-A325CPI | Peripheral Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W942508BH | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM |

| W942508CH | 制造商:WINBOND 制造商全稱:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM |

| W942508CH-5 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM |

| W942508CH-6 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM |

| W942508CH-7 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:8M x 4 BANKS x 8 BIT DDR SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。