- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382377 > PCA5007H (NXP Semiconductors N.V.) Pager baseband controller PDF資料下載

參數(shù)資料

| 型號: | PCA5007H |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Pager baseband controller |

| 中文描述: | 傳呼機(jī)基帶控制器 |

| 文件頁數(shù): | 50/112頁 |

| 文件大小: | 604K |

| 代理商: | PCA5007H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

1998 Oct 07

50

Philips Semiconductors

Product specification

Pager baseband controller

PCA5007

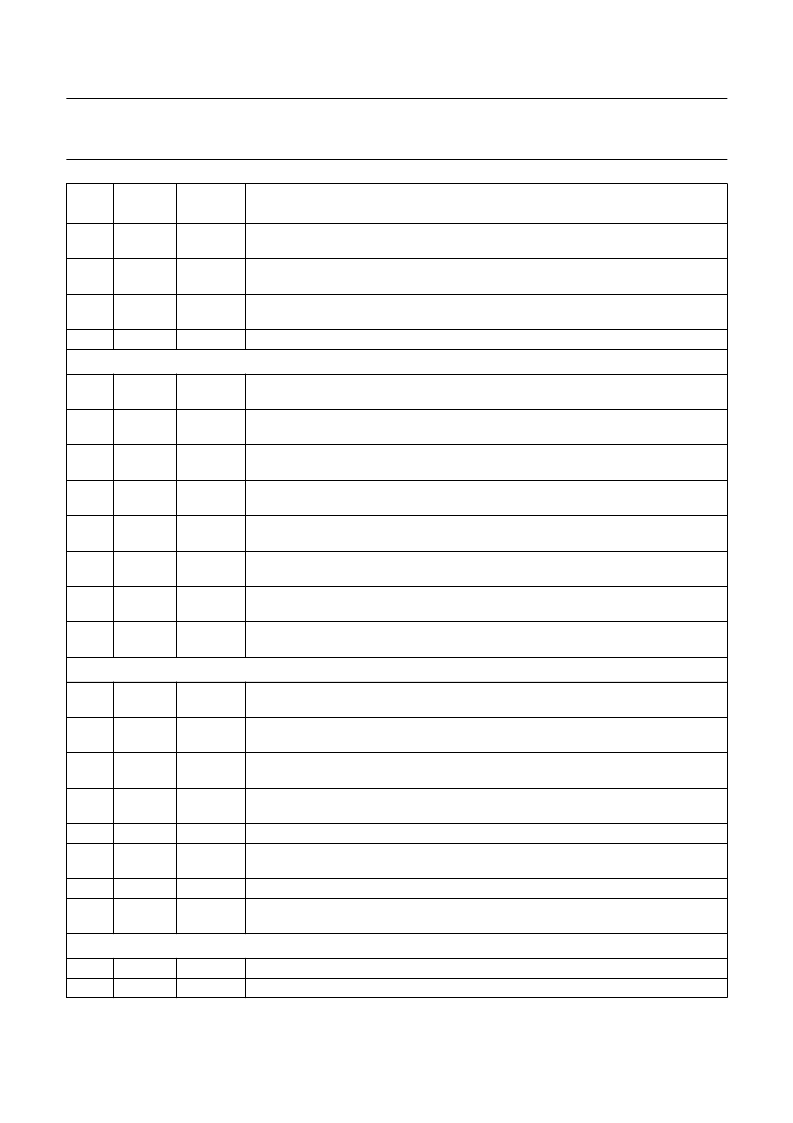

4

PS0

UART

Defines the UART interrupt priority level. PS0 = 1 programs it to the higher priority

level.

Defines the I

2

C-bus interrupt priority level. PS1 = 1 programs it to the higher priority

level.

WAKE-UP Defines the WAKE-UP interrupt priority level. PT2 = 1 programs it to the higher

priority level.

/

unused

5

PS1

I

2

C

6

PT2

7

IP1 address F8H: interrupt priority for X2 to X9

(note 2)

0

PX2

P1.0

Defines the EXTERNAL2 interrupt priority level 1. PX2 = 1 programs it to the higher

priority level.

Defines the EXTERNAL3 interrupt priority level 1. PX3 = 1 programs it to the higher

priority level.

Defines the EXTERNAL4 interrupt priority level 1. PX4 = 1 programs it to the higher

priority level.

Defines the SYMBOL interrupt priority level 1. PX5 = 1 programs it to the higher

priority level.

Defines the EXTERNAL6 interrupt priority level 1. PX6 = 1 programs it to the higher

priority level.

Defines the DC/DC CONVERTER interrupt priority level 1. PX7 = 1 programs it to the

higher priority level.

Defines the WATCHDOG interrupt priority level 1. PX8 = 1 programs it to the higher

priority level.

Defines the REAL-TIME CLOCK interrupt priority level 1. PX9 = 1 programs it to the

higher priority level.

1

PX3

P1.1

2

PX4

P1.2

3

PX5

SYMBOL

4

PX6

P1.4

5

PX7

DC/DC

6

PX8

WDI

7

PX9

MIN

TCON address 88H: timer/counter mode control register

0

IT0

P3.2

EXTERNAL0 interrupt type control bit

. Set/cleared by software to specify falling

edge/low level triggered external interrupt.

EXTERNAL0 interrupt flag

. Set by hardware when external Interrupt detected.

Cleared by hardware.

EXTERNAL1 interrupt type control bit

. Set/cleared by software to specify falling

edge/low level triggered external interrupt.

EXTERNAL1 interrupt flag

. Set by hardware when external Interrupt detected.

Cleared by hardware.

Timer 0 run control bit

. Set/cleared by software to turn timer on/off.

Timer 0 overflow flag

. Set by hardware on timer/counter overflow. Cleared by

hardware or software.

Timer 1 run control bit

. Set/cleared by software to turn timer on/off.

Timer 1 overflow flag

. Set by hardware on timer/counter overflow. Cleared by

hardware or software.

1

IE0

P3.2

2

IT1

P3.3

3

IE1

P3.3

4

5

TR0

TF0

TIMER 0

TIMER 0

6

7

TR1

TF1

TIMER 1

TIMER 1

IRQ1 address C0H: interrupt request register for X2 to X9

0

1

IQ2

IQ3

P1.0

P1.1

Interrupt request flag from P1.0.

Interrupt request flag from P1.1.

BITS

CONV.

NAME

SOURCE

NOTES

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCA5010 | Pager baseband controller |

| PCA5010H | Pager baseband controller |

| PCA82C200 | STAND-ALONE CAN-CONTROLLER |

| PCA82C200P | STAND-ALONE CAN-CONTROLLER |

| PCA82C200T | STAND-ALONE CAN-CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCA5007H/XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| PCA5010 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Pager baseband controller |

| PCA5010H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Pager baseband controller |

| PCA5010H/XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|8051 CPU|CMOS|QFP|48PIN|PLASTIC |

| PCA503HL320 | 制造商:ADAM-TECH 制造商全稱:Adam Technologies, Inc. 功能描述:ZIF FLEX CIRCUIT CONNECTOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。