- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384797 > OR4E10 (Lineage Power) Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) PDF資料下載

參數(shù)資料

| 型號: | OR4E10 |

| 廠商: | Lineage Power |

| 英文描述: | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| 中文描述: | 現(xiàn)場可編程門陣列(現(xiàn)場可編程門陣列) |

| 文件頁數(shù): | 81/132頁 |

| 文件大小: | 2667K |

| 代理商: | OR4E10 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁當前第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁

Lucent Technologies Inc.

81

Preliminary Data Sheet

August 2000

ORCA Series 4 FPGAs

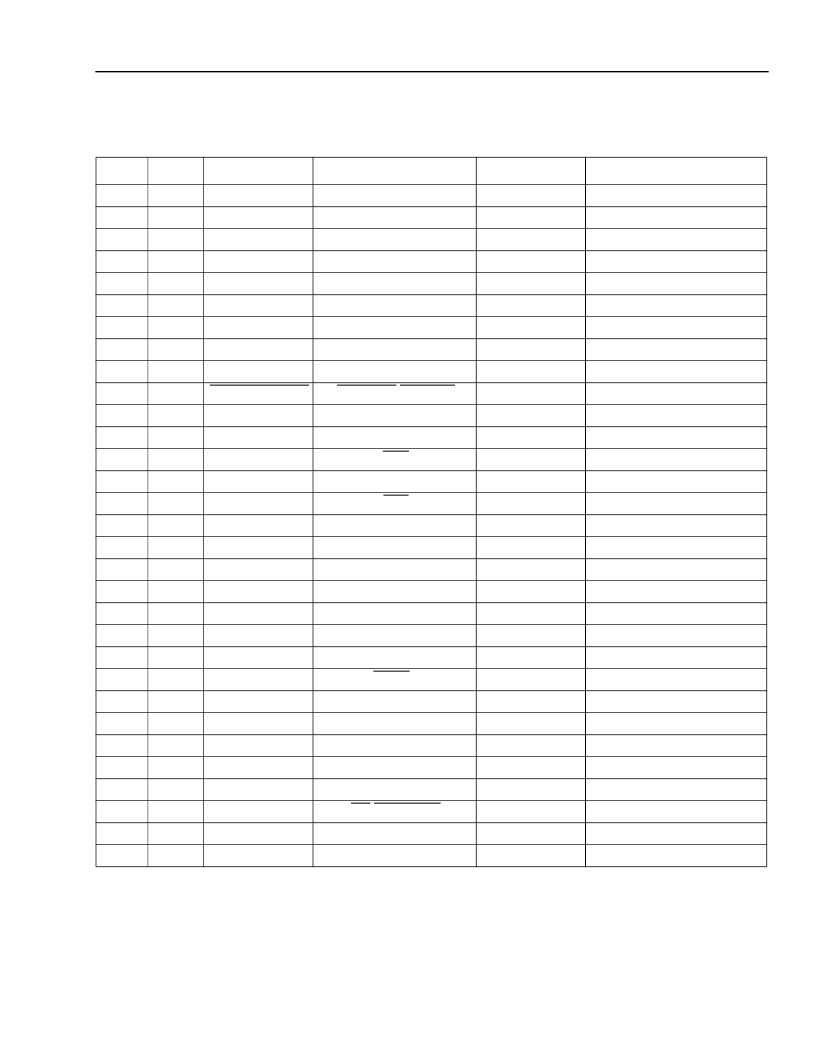

Ball

Bank

Pad

Function

Pair*

Differential

AD4

AF4

AE5

AC5

AF5

AE6

AC7

AD6

B3

C5

C4

J4

H2

H3

H1

J1

J2

J3

K2

K4

K1

K3

L2

M1

M2

N2

L3

N1

M4

P2

M3

BL

BL

BL

BL

BL

BL

BL

BL

TL

TL

TL

TL

TL

TL

TL

TL

TL

CL

CL

CL

CL

CL

CL

CL

CL

CL

CL

CL

CL

CL

CL

PB4C

PB4D

PB6C

PB6D

PB8C

PB8D

PB9C

PB9D

PCCLK

VREF

DP3

VREF

D14

D15

D16

D17

D18

CCLK

L7T_A1

L7C_A1

L8T_A1

L8C_A1

L9T_D0

L9C_D0

L10T_D0

L10C_D0

—

—

—

L17T_D1

L17C_D1

L18T_A1

L18C_A1

L19T_A0

L19C_A0

L1T_D0

L1C_D0

L2T_A2

L2C_A2

L3T_D0

L3C_D0

L4T_A0

L4C_A0

L5T_D1

L5C_D1

L6T_D2

L6C_D2

L7T_D1

L7C_D1

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

—

—

—

PCFG_MPI_IRQ

PDONE

PL10C

PL10D

PL12C

PL12D

PL13C

PL13D

PL14C

PL14D

PL16C

PL16D

PL18C

PL18D

PL19C

PL19D

PL21C

PL21D

PL23C

PL23D

PL24C

PL24D

CFG_IRQ/MPI_IRQ

DONE

CS1

CS0

DOUT

INIT

A16

VREF

A14

A15

D4

VREF

VREF

RDY/BUSY/RCLK

A12

A13

VREF

A11

VREF

RD/MPI_STRB

PLCK0T/SCKA

PLCK0C

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

TRUE

COMPLEMENT

Pin Information

(continued)

Table 44. OR4E6 352-Pin PBGA Pinout

(continued)

* Differential pairs and physical locations are numbered within each bank (e.g., L19C_A0 is ninteenth pair in an associated bank). The C indi-

cates complementary differential whereas a T indicates true differential. The _A0 indicates the physical location is adjacent balls in either hor-

zontal/vertical direction. Other physical indicators are as follows:

_A1 indicates one ball between pairs.

_A2 indicates two balls between pairs.

_D0 indicates balls are diagonally adjacent.

_D1 indicates diagonally adjacent separated by one physical ball.

相關PDF資料 |

PDF描述 |

|---|---|

| OR4E14 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| OR4E2 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| OR4E4 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| OR4E6 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| ORT4622 | Field-Programmable System Chip (FPSC) Four Channel x 622 Mbits/s Backplane Transceiver(現(xiàn)場可編程系統(tǒng)芯片(四通道x 622 M位/秒背板收發(fā)器)) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| OR4E14 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| OR4E2 | 制造商:AGERE 制造商全稱:AGERE 功能描述:Field-Programmable Gate Arrays |

| OR4E2-1BA256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E2-1BA352 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E2-1BA416 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。